- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Kinetis: Using OSERCLK with High Range Crystal (8-32 MHz)

Kinetis: Using OSERCLK with High Range Crystal (8-32 MHz)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Kinetis: Using OSERCLK with High Range Crystal (8-32 MHz)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

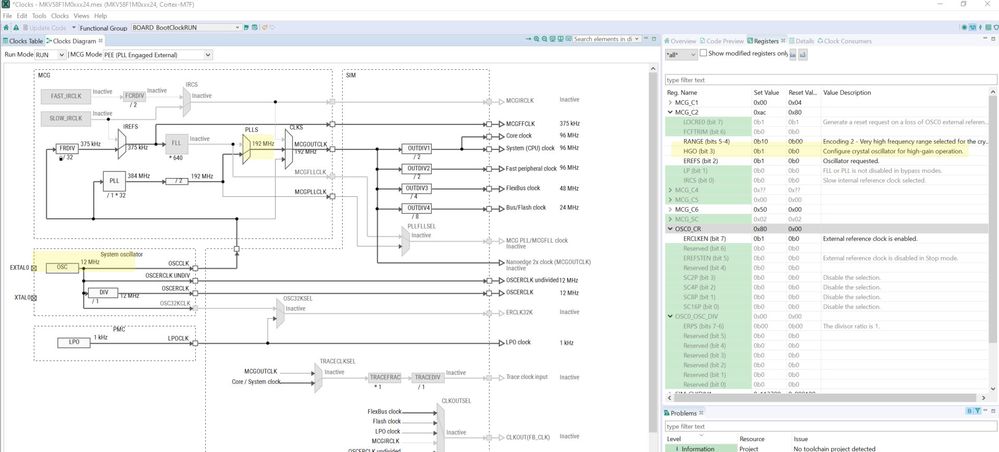

Using either KV58 (MKV58F1M0VLQ24) or K22 (MK22FX512AVLQ12), I ran into a common issue where it appears that Boot Clock initialization call CLOCK_BootToPeeMode() fails only if I attempt to enable OSERCLK while using a 12 MHz crystal in high gain mode. 12 MHz crystal was connected to MCU only with 1 Mohm resistor (Rf) in parallel. In both cases the PLL was configured to drive processor clock no faster than 120 MHz.

Without paying too much attention, workarounds used included steps to:

- Disable and avoid OSERCLK altogether, using HF External Oscillator in High Gain Mode, or

- Enable OSERCLK, using HF External Oscillator in Low Power Mode

What is difference between using External Oscillator in Low Power Mode vs. High Gain Mode?

Why can't OSERCLK be enabled using 12 MHz External Oscillator in High Gain Mode?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Using 12 MHz crystal in High Gain mode, if I try enabling OSERCLK, then function call CLOCK_BootToPeeMode() always gets stuck in below section of code:

MCG->C1 = (MCG->C1 & ~MCG_C1_CLKS_MASK) | MCG_C1_CLKS(kMCG_ClkOutSrcOut);

while (MCG_S_CLKST_VAL != kMCG_ClkOutStatPll)

{

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi lsrbigfoot,

Which IDE you are using?

If you are using the MCUXPresso IDE, you can check the clock diagram, whether your PLL output is in the 110Mhz to 240Mhz range.

From your stuck point, it is related to the PLL is not locked OK.

You also can check the related PLL factor, whether the output will exceed the datasheet's range or not.

After you enable the load capacitor, it has the improvement, whether the issue can be solved?

Wish it helps you!

If you still have questions about it, please kindly let me know!

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-----------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi lsrbigfoot,

Oscillator crystal or resonator frequency — high frequency mode (high range) (MCG_C2[RANGE]=1x) is 8Mhz to 32Mhz.

Your 12Mhz is the high frequency, if you use the high gain mode(HGO=1), then the feedback is 1M resistor.

About the different OSC module modes, please check the chip reference manual, take K22 as an example, please check chapter 26.8.2 OSC module modes.

26.8.2.3 High-Frequency, High-Gain Mode

In high-frequency, high-gain mode, the oscillator uses a simple inverter-style amplifier.

The gain is set to achieve rail-to-rail oscillation amplitudes. This mode provides low pass

frequency filtering as well as hysteresis for voltage filtering and converts the output to

logic levels. In this mode, the internal capacitors could be used.

26.8.2.4 High-Frequency, Low-Power Mode

In high-frequency, low-power mode, the oscillator uses a gain control loop to minimize

power consumption. As the oscillation amplitude increases, the amplifier current is

reduced. This continues until a desired amplitude is achieved at steady-state. In this

mode, the internal capacitors could be used, the internal feedback resistor is connected,

and no external resistor should be used.

The oscillator input buffer in this mode is differential. It provides low pass frequency

filtering as well as hysteresis for voltage filtering and converts the output to logic levels.

When you have issues, do you check your crystal pin, whether it is oscillating or not?

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------