- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- KEA64 SPI Communication problem

KEA64 SPI Communication problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

KEA64 SPI Communication problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

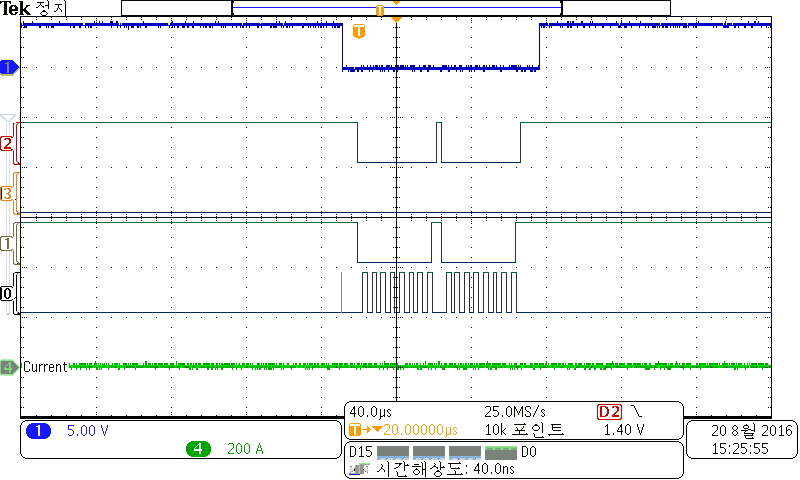

Enviroment : KEA64 EVB Kit --> Onsemi LED Driver with SPI Communication

Tool : KDS with P.E

Problem : The SS pin just one byte continue low state

Must be "SS Pin" to continue Turn Low (until complete 2byte)

I know that is Clock phase setting "Change on leading edge"

Then I can chip selecting togging " No"

Unfortunately, My target PCB can`t read

when I setup [Clock phase setting : “Change on leading edge"]

So I tried Clock phase setting “Capture on Leading edge”

then [chip selecting togging " Yes" ]

And Other a GPIO port setting Output

A GPIO port use to connecting target B.D SS port

The GPIO port sync to SPI communication time domain

then I can transferdata.

I want to setup Clock phase setting "Change on leading edge" & chip selecting togging " No"

How can I setting above my desire ?

Please look below my picture

Blue line : GPIO out

Line No2 : SS pin

Line No3 : MISO

Line No1: MOSI

Line No0: CLK

"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Ahn,

In order to send more than 8 bits as the same transaction SS must not be controlled by SPI module, otherwise, SPI module will driver high this signal once 8 bits are sent. KEAxxx has the hability to manage SS signal by GPIO for these kind of use cases.

In this post, there is a similar issue (user wants to receive more than 8 bits per transaction) and SPI code for sending 16-bits data is provided: https://community.nxp.com/thread/358663

I hope this helps!

Regards,

Isaac