- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- K70F150M and external 12MHz oscillator

K70F150M and external 12MHz oscillator

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all. I'm trying to initialize K70F150M, which uses external 12MHz oscillator at XTAL1 and external XTAL32 32kHz.

MCGOUTCLK supposed to be 150 MHz, target mode - PEE, selected PLL - PLL0.

I want initialize k70 like in it's datasheet, example #1

Here are my modes sequency: FEI-> FBE-> PBE-> PEE.

Here are PLL0 frequency dividers:

12MHz * 1 * 25 = 150 MHz, so

PRDIV0=0x00u

VDIV0 = 0x09u

I have a problem configuring C1

Example text: "C1[FRDIV] set to 3'b100, or divide-by-512 because 8 MHz / 512 = 31.25 kHz which is in the 31.25 kHz to 39.0625 kHz range required by the FLL."

But I have 12 MHz oscillator, so 12 Mhz / 512 = 23.4kHz, 12MHz/256=46.8kHz

So I don't have any dividers to get frequency in the secified range. What value I have to set in?

Whole initialization code is in attachment #1

Example's screenshot are in the attachments #2 and #3.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Why? I'm trying to use external clock, not the crystal.

You are right, for a moment I thought of the crystal on the tower board.

Still pay attention to MCG->S2 (only the first, not all) and OUTDIV4.

As for the board not working, let's wait for your new boards, or you can always post a new thread describing your issue.

Regards,

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alexander:

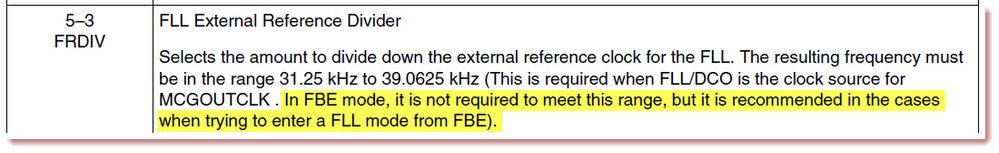

Your crystal will not allow you to match the required FLL input range. But in FBE mode the FLL is bypassed, so you can ignore the restriction. Just keep the reference as close as possible, in this case I would go with the 512 divider (ref_clk = 23.4 kHz).

Be aware that due to this situation, you will not be able to use the FLL output, so you cannot enter FEE mode.

In the reference manual you have this:

Hope this helps!

/Jorge Gonzalez

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So, I still need 150MHz at system clock.

In FBE mode, I have to set C1[CLKS] to 10(binari).

So according to datasheet,

10 Encoding 2 — External reference clock is selected.

It means that both core/system clock and bus clock will be max 12 MHz?

Yep, I can get 150 MHz at PLL0 for peripherals, but system/core clock is too small.

Am i right?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In FBE mode your max frequency would be 12 MHz. But you can continue switching to PBE and then to PEE, so you get your 150 MHz.

Your init code seems good to me, except for line #203.

It is:

MCG->C5 = (uint8_t)(MCG_C5_PLLREFSEL0MASK | MCG_C5_PRDIV0(0x01) ); // 0x01 -> divider = 2;

I think this should be:

MCG->C5 = (uint8_t)0x00U; // PLLREFSEL0 = 0, OSC0 as reference; PRDIV0 = 0, 12 MHZ/1 = 12 MHZ

You mentioned about using XTAL1, was that a typo? Because your code shows you use XTAL0 and EXTAL0, corresponding to OSC0.

Regards!

Jorge Gonzalez

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Jorge.

XTAL1 wasn't a typo.

Datasheet, MCG_C5 field descriptions:

PLLREFSEL0 - PLL0 External Reference Select

Selects PLL0 external reference clock source.

0 Selects OSC0 clock source as its external reference clock.

1 Selects OSC1 clock source as its external reference clock.

You say: "Because your code shows you use XTAL0 and EXTAL0, corresponding to OSC0."

Did you see using OSC0 anywhere else? I'm asking because it seems that my eyes are not able to find any more errors in code :smileyhappy:

Best regards, Alexander.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alexander:

So, I am a bit confused. Your init code is oriented to OSC0. Attached is your image with a pair of lines highlighted. Besides you have code for PLL1 (C11, C12), what is that for?

Now, if you don't have a crystal for OSC0, that might be a problem. In the path (FEI -> FBE -> PBE -> PEE), the FBE and PBE modes require an external clock, and such external clock can only be OSC0 or RTC, not OSC1. So, if you want to pass through those modes without using OSC0, then you need RTC as external clock (MCG_C7[OSCSEL] = 1).

Just to be clear, are we talking about a custom board, or tower board?

Regards!

Jorge Gonzalez

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After reconfig I've got "device could not be powered up" message...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

:smileyalert: EDIT: The actual tower board is TWR-K70F120, with a 120 MHz MCU. Are you trying 150 MHz on that? You could damage the device. Or am I missing something?

You are welcome.

Where do you see that message? Console, pop-up window, terminal?

Could you please show me your fixed code?

/Jorge

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Jorge

Situation is still the same - board is not responding.

So right now I am waiting for next delivery of boards.

Jorge, couldn't you explain me, how wrong frequency parameter, which is set by software, is able to damage a hardware?

And what can you say about fixed code?

Best regards, Alexander

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alexander:

The clock settings in software are reflected in the internal hardware clock, in this case the clock sourced to the core. So if you configure the core clock to be 150 MHz in a 120 MHz device, then you are forcing the MCU out of specifications, and it is not guaranteed.

I found a thread with a similar error message like yours, and it had something to do with the high gain setting:

FRDM-KL25Z: Device could not be powered up.

I do not think this is your case, but try playing with the HGO bit configuration.

And sorry, lately I am a bit stuck and have not verified your last code, but as soon as I check it I will let you know.

Regards!

Jorge Gonzalez

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jorge.

So, I have 3.3V at VOUT33, and 1.8V at DDR_VDD1-DDR_VDD10, PK70FN1M0VMJ15 is powered.

But I haven't any signal at EXTAL1.

Neither low-level signal at nReset-IN nor anything else gave result.

Does it means that MPU is dead? If so, am I right: is there no internal protection from changing of frequency multipliers by the programmer?

Do you know any other way how to reset MPU's registers at the default state?

P.S. I still wanna know, what about my code :smileyhappy:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alexander:

I am sorry for the delay, this week I am very busy.

I checked your code and detected the next problems:

- :smileyalert: SIM_CLKDIV1_OUTDIV4(0). This is not good, it sets a divider of 1 for the flash clock. You are configuring a 150 MHz PLL output. Flash maximum clock is 25 MHz.

- MCG_C10[EREFS1] should be 1. You are using crystal, not external reference clock.

- while((MCG->S2 & MCG_S2_OSCINIT1 ... ) Change S to S2

I do not know of any internal frequency protection, so it is programmer responsibility not to exceed the limits.

If your device is not dead, at the very least you should be able to do a mass erase. Have you tried that?

Regards,

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Jorge.

Yes, I've tried. It didn't gave any effect. Now I'm talking to manufacturer about that.

>>>>MCG_C10[EREFS1] should be 1. You are using crystal, not external reference clock.

Why? I'm trying to use external clock, not the crystal.

Best regards, Alexander.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Why? I'm trying to use external clock, not the crystal.

You are right, for a moment I thought of the crystal on the tower board.

Still pay attention to MCG->S2 (only the first, not all) and OUTDIV4.

As for the board not working, let's wait for your new boards, or you can always post a new thread describing your issue.

Regards,

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, Jorge, thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi again Alexander:

Something just came to my mind. If you use external clock instead of crystal, then there is no reason to wait for OSCINIT1 flag. I think it would actually block execution. Remove the first while loop.

Regards,

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jorge.

We are talking about tower board, k70f150m.

Errors c2->c10 and pll1->osc0 are already fixed(code for pll1 is deleted).

A lot of thanks for MCG_S2_OSCINIT1 bit, I didn't see it.

It explains a lot of problems.

Best regards, Alexander.