- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: K60 USB High Speed ULPI Clock

K60 USB High Speed ULPI Clock

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

K60 USB High Speed ULPI Clock

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello.

Could someone clarify how clocking for USB HS module on K60 actually works?

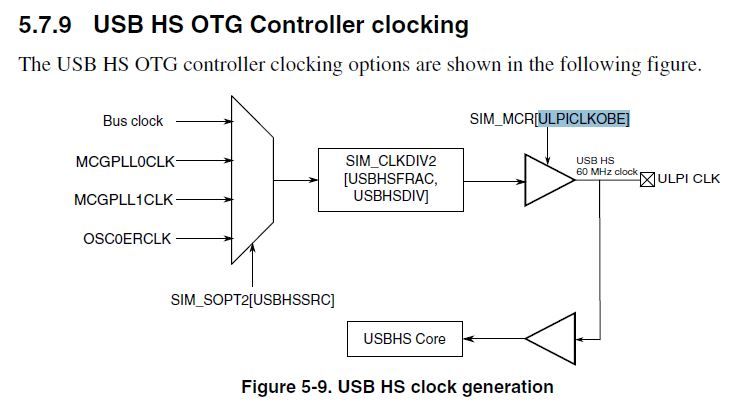

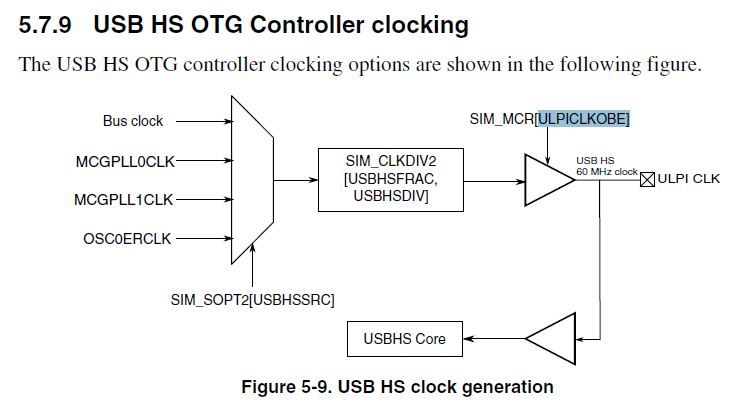

- Device clock summary (in the reference manual K60P144M150SF3RM) states that clock source for USB HS module can be one of the following: "Bus clock, MCGPLL0CLK, MCGPLL1CLK, or OSC0ERCLK with fractional clock divider, or ULPI_CLK".

- In signal description tables (in the signal descriptions chapter and in the USB HS module description chapter) ULPI_CLK is shown as input only pin.

- USB HS OTG Controller clocking mentions SIM_MCR[ULPICLKOBE] flag that is not present in the SIM chapter but is mentioned in the revision history: "In the MCR register, updated the ULPICLKOBE field description to be reserved.".

- In the revision 2 of the same reference manual, there is a description for aforementioned flag:

- 0 Internal generated 60MHz ULPI clock is not output to the ULPI_CLK pin.

- 1 Interanl generated 60MHz ULPI clock provide clock for external ULPI phy.

- I am using TWR-K60F120M board and when I configure USB HS clock (bare metal, curiously enough, that flag is defined in the MK60F12.h header provided with the KDS) and set the flag, I can confirm with oscilloscope that the 60MHz output is present on the pin.

- Unfortunately, I don't have a SER2 module or any ULPI transceiver at the moment, but from the data sheet for USB3300 I learned that it only outputs 60MHz and can't use external 60MHz reference. Also, it seems that people who've used USB HS with SER2 had no problems.

- In the module clocks table in the "Clock Distribution" chapter, ULPI_CLK is in the I/O interface clocks column, and USB HS clock (that is described as internal clock or ULPI_CLK in the device clock summary) is in the internal clocks column.

My first question is, does USB HS module use ULPI_CLK input in any way? Or, in other words, does ULPICLKOBE determine not only whether the internal clock will be output but also whether external clock will be used or internal one.

Can I use a different transceiver that uses ULPI_CLK as input and generate the clock in the MCU and provide it to the transceiver using ULPICLKOBE? (or was it removed from the reference manual because it shouldn't be used?)

And the last question, if USB HS module does not use ULPI_CLK input at all then could there be problems caused by phase mismatch between transceiver and the module?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Grigorii,

I think I need some times to confirm with the AE team about this issue and reply you later.

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am just fighting with the same problem: not clear where is the SIM_MCR[ULPICKOBE] bit : as it is already mentioned in this thread, the Appendix of rev. 3 says that this field was updated to be "reserved", so even if I should set it to 0, according to jeremyzhou, I don't see how can I do it.... Neither clear the meaning of "ignore the USBHSRC bits" ... does it mean that if I would like to use the USB_HS interface, I must use external clock source ? Could someone educate me, please ?

Thanks and regards

Tibor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tibor

The K60 HS USB must be used with an external 60MHz clock (supplied by the external PHY).

It is not necessary to write to the SIM_MCR register since the clock output should not be enabled (it defaults to input).

SIM_SOPT2 (containing an option for a local HS USB clock source) is not relevant since it is never used. This register also doesn't need to be used for K60 HS USB.

Regards

Mark

Kinetis for professionals: http://www.utasker.com/kinetis.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark,

Thank you for the clarification.

Cheers

Tibor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

--- EDITED on Apr 29, 2015 ---

Q. My first question is, does USB HS module use ULPI_CLK input in any way? Or, in other words, does ULPICLKOBE determine not only whether the internal clock will be output but also whether external clock will be used or internal one.

- Since ULPICLKOBE has been changed to reserved, that means internal clock is NOT suggested to be used for USB HS module (default value of ULPICLKIBE=0, the clock buffer is disable). By looking at Fig.5-9, you can see how the ULPI CLK works.

Q. Can I use a different transceiver that uses ULPI_CLK as input and generate the clock in the MCU and provide it to the transceiver using ULPICLKOBE? (or was it removed from the reference manual because it shouldn't be used?)

- I think it should not be used as you said it was removed from the RM.

Q. And the last question, if USB HS module does not use ULPI_CLK input at all then could there be problems caused by phase mismatch between transceiver and the module?

- no idea

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

derek lau wrote:

Q. My first question is, does USB HS module use ULPI_CLK input in any way? Or, in other words, does ULPICLKOBE determine not only whether the internal clock will be output but also whether external clock will be used or internal one.

- Since ULPICLKOBE has been changed to reserved, that means internal clock is suggested to be used for USB HS module. By looking at Fig.5-9, you can see how the ULPI CLK works.

Yeah, I've seen this picture but I am not completely sure that ULPI CLK is bidirectional: judging by the way it is shown it appears as if unless ULPICLKOBE is set, the USBHS Core will not use internally generated clock at all and will use ULPI CLK input instead.

Anyway, I've also found this in the SIM_MCR description in the AN4526 ("Kinetis 100 MHz Rev 1.x to 120 MHz Migration Guide"): "This module has fields for:... ULPI clock direction". Though, I still would like to hear confirmation from Freescale that when ULPI CLK is used as input USB HS Core will synchronize I/O on it and not on the internal clock signal.

Also, would be nice to know why the field was removed and whether internal clock is used at all when the external is present (the figure shows only one clock).

If I had a transceiver, I'd check the latter by setting USBHSFRAC/USBHSDIV to incorrect frequency and looking if the transmission would break or not.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Grigorii,

For now, I'd like to suggest that you'd better to configure the SIM_MCR[ULPICKOBE] bit to be cleared, then ULPI_CLK as an input to the MCU.

You can ignore the the USBHSRC bits. I think theses bits will be removed in later versions of the manual.

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I was wondering something along the same. I'm looking at a USB-ULPI for the MK20Fxxx120Mhz and newbie to ULPI. The USB3300 is used on TWR-SCH2

It seems like the ULPI_CLK is from USB3300 to processor. and the USB3300 requires a seperate 24Mhz clock

Looking at the followingTWR-SCH2 schematic SCH-26185

Enhanced Serial (Dual Ethernet, High-Speed US|Freescale

Seems like the USB3300 has a 24Mhz xtal - and I was wondering if this can be generated on the main processor - part of CLKOUT?

Also I was wondering if anybody knows the lowering power USB3320 could be used - has internal oscillator with PLL and a variety of clock inputs, and different pinout. Software compatibility is essential.

Many thanks.