- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- K22: External 4 MHz osc, 31.25 kHz in FLL clock requirement concerns

K22: External 4 MHz osc, 31.25 kHz in FLL clock requirement concerns

Hi,

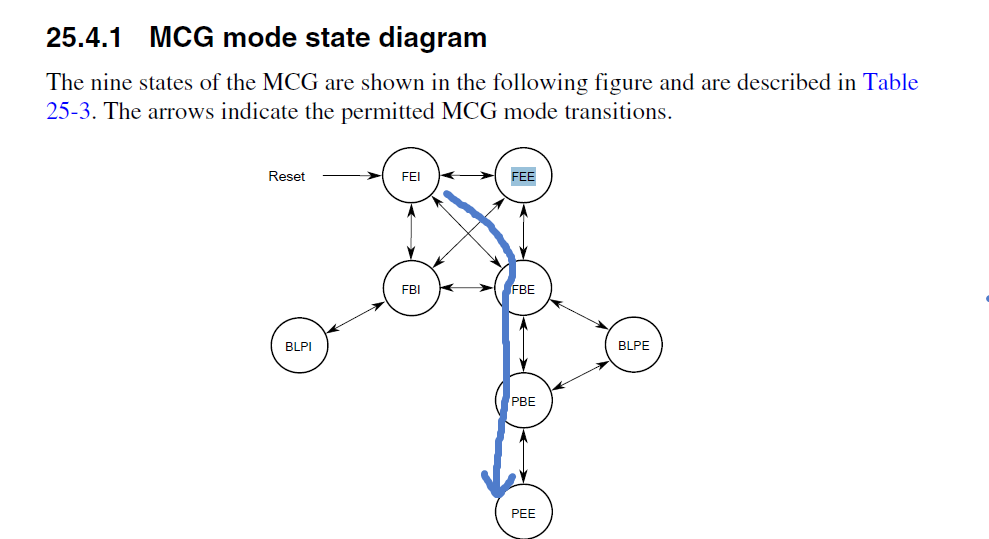

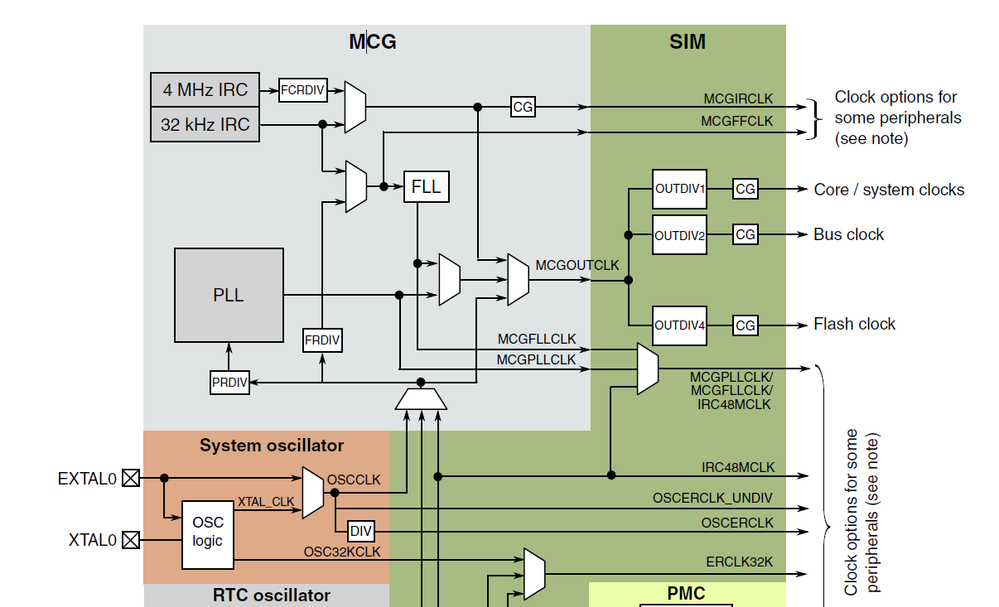

My design using the K22 (MK22FN256VLL12) involves using an external clock running at 4 MHz. It's a resonator. I want to transition from FEI until PEE mode, which also involves the intermediate transition to FEE mode. It is basically described by example 1 in section 25.5.3.1, except my final MCGOUTCLK is 120 MHz.

My setup works well, but my worry is the requirement that in FEE and FEI modes, the FLL reference clock must be defined by scaling the input clock using FRDIV. When using 4 MHz, the only suitable value for FRDIV is 128, yielding 31.250 kHz. This is the absolute rock bottom end of the allowed range, and my worries is that with aging and slight temperature drift, the 4 MHz may have decreased by e.g. 2%, thus absolutely not meeting the requirement.

I couldn't find anywhere in the reference manual where this is mentioned, and the example also assumes that 4 MHz is used, as if there would never be any issue in doing so.

My questions:

1) What would happen, if FLL decreases below 31.250 kHz?

2) If there is a problem, is the only solution to go with a higher freq oscillator, e.g. 4.19 MHz which seems to be very common?

If yes to 2), there's one more question:

3) The internal fast clock is also 4 MHz, with a 5% tolerance - what is the purpose of this, when it could potentially also result in an FLL frequency lower than 31.250 kHz?

Hopefully, I've missed something :-)

Thanks for any help.

已解决! 转到解答。

Hi

Take a look at http://www.utasker.com/kinetis/MCG.html for a further discussion of MCG.

Regards

Mark

Kinetis: http://www.utasker.com/kinetis.html

Kinetis K22:

- http://www.utasker.com/kinetis/FRDM-K22F.html

- http://www.utasker.com/kinetis/TWR-K22F120M.html

- http://www.utasker.com/kinetis/BLAZE_K22.html

- http://www.utasker.com/kinetis/tinyK22.html

Free Open Source solution: https://github.com/uTasker/uTasker-Kinetis

Working project in 15 minutes video: https://youtu.be/K8ScSgpgQ6M

For better, faster, cheaper product developments consider the uTasker developer's version, professional Kinetis support, one-on-one training and complete fast-track project solutions to set you apart from the herd : http://www.utasker.com/support.html

Hi Customer,

Answer your 3 questions:

1) What would happen, if FLL decreases below 31.250 kHz?

Answer: The K22 datasheet although shows the min. FLL reference clock is 31.25KHz, there also with the clock tolerance of this frequency in MCG module design.

While, there is an errata item about MCG FLL clock, more detailed info please check below document:

e7993: MCG: FLL frequency may be incorrect after changing the FLL reference clock

http://cache.nxp.com/files/32bit/doc/errata/KINETIS100MHZ_0N74K.pdf

Actually, the external crystal normally is more precise than the internal IRC, take the ABRACON crystal as an sample, the max data is 100ppm, aging at 25°C/year is about 5ppm. this still very low, I think if it reach 2% error rate, that crystal is not precise enough. If you care more about the error rate, you can select the precise ppm crystal, and the stable crystal. About the clock below 31.25Khz, I think the normal crystal error rate is in our MCU tolerance.

2) If there is a problem, is the only solution to go with a higher freq oscillator, e.g. 4.19 MHz which seems to be very common?

If yes to 2), there's one more question:

Answer: Because the MCU clock have tolerance, even the datasheet didn't give the detail data, but the normal crystal should be enough to use. But one point need to take care, if the error rate is too high, the FLL may can't be locked, it will cause indeterminate behavior.

Actually, you are using PLL, you totally can don't use FEE, you can follow this way:

3) The internal fast clock is also 4 MHz, with a 5% tolerance - what is the purpose of this, when it could potentially also result in an FLL frequency lower than 31.250 kHz?

Answer: 4Mhz IRC can't be used as the FLL input:

Wish it helps you!

If you meet the real practical question about this topic, please also kindly let me know!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Kerry,

Thanks a lot for your answer, it is much appreciated. Actually, upon further inspection, I already do the transition directly from FEI to FBE, bypassing FEE completely.. oops. :smileyhappy:

But regardless of this, FBE mode, which is mandatory to ever get to a PEE mode requires that the the FLL is enabled, albeit not used. According to for example table 25-3 of the reference manual, the 31.25-39.0625 kHz requirement still applies, but I don't understand why, when it is not used.

I guess you're right that there must still be some variance with the 31.25 kHz, but as the fast IRC cannot be used, then there's no guarantee it is 5%, maybe 2% which is the precision for the slow IRC. So as there is no guarantee of anything, I think we'll switch to a 4.19 MHz external osc. I suppose there are no other options, when I want to run in PLL clock mode?

Hi

Take a look at http://www.utasker.com/kinetis/MCG.html for a further discussion of MCG.

Regards

Mark

Kinetis: http://www.utasker.com/kinetis.html

Kinetis K22:

- http://www.utasker.com/kinetis/FRDM-K22F.html

- http://www.utasker.com/kinetis/TWR-K22F120M.html

- http://www.utasker.com/kinetis/BLAZE_K22.html

- http://www.utasker.com/kinetis/tinyK22.html

Free Open Source solution: https://github.com/uTasker/uTasker-Kinetis

Working project in 15 minutes video: https://youtu.be/K8ScSgpgQ6M

For better, faster, cheaper product developments consider the uTasker developer's version, professional Kinetis support, one-on-one training and complete fast-track project solutions to set you apart from the herd : http://www.utasker.com/support.html

Hi Mark,

Thanks a lot, it is indeed very helpful. I did try to change FRDIV while transitioning to FBE mode, and no matter what value it was dividing by, it did work well with the 4 MHz external osc. That is, it did switch to the external oscillator, i.e. IREFST is set to 0.

You write that "The FLL will continue oscillating at its own resonance frequency since it can't lock to one defined by the source." Not that I doubt you at all, but have you been able to verify this by readout of any specific registers, or are you able to measure the FLL directly somehow?

Kind regards,

Troels

Troels

It is possible to set up FLL operation and remove its clock source and it will continue running. If the FLL is being used as system clock its can be measured indirectly almost everywhere....

In comparison, PLL will fail if its clock source is removed.

The FLL seems too be like a fly-wheel in an engine that keeps going under its own momentum.

When switching between states internally one tries to keep the FLL input within its range but it is not particularly critical if the FLL output is not being used in the sequence anyway.

Regards

Mark