- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- K10 ADC Calibration

K10 ADC Calibration

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

K10 ADC Calibration

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

We are encountering an issue with the calibration of ADC peripheral (Kinetis MK10DX128VLH5).

Issue Summary:

On some PCBA, we figured out that a cold start (regarding power supply) leads to ADC conversion errors (around 3%)

After investigation, it seems that the issue comes from ADC calibration.

With a hot start, there is no conversion error è Calibration is OK

With a cold start, conversion error is around 3% è Calibration seems to be inaccurate

Note:

- Hot start = VCC is removed and put again while UART is connected to computer

- Cold start = VCC is removed and put again while UART is not connected to computer

Figures:

Gain and offset calibration data have been logged and compared.

Hot start :

PG=0x81B1 = 1.013214111

MG=0x8000

OFS=0x1F

Conversion Result = 3696

Cold start :

PG=0x823E = 1.01751709

MG=801F

OFS=0x1F

Conversion Result = 3814

Error (Conversion Result) = (3814/3696-1)x100 = 3.2%

Ratio (Gain calibration data) = (1.0175/1.0132-1)x100 = 0.42%

Gain calibration data are very close but conversion results are farther. Is it the right calculation ?

Conditions:

- VREF peripheral is initialized and enabled

- Wait that VREFST flag is set in VREF_SC register

- Initialize ADC peripheral

- Start ADC calibration

We have noticed that waiting a few time between VREFST is set and start of calibration solves the issue.

So, we wonder if calibration is impacted by VREF peripheral and if it is recommended to wait some time before starting calibration.

Note:

Calibration is not done in the conditions mentioned in the reference manual.

Calibration is done with an ADC clock of 10Mhz, no averaging and VCC is rising.

Register Values:

VREF_SC = 0xE1 = VREF_SC_VREFEN_MASK | VREF_SC_REGEN_MASK | VREF_SC_ICOMPEN_MASK | VREF_SC_MODE_LV(1)

ADC0_CFG1 = 0x00000094 = ADC_CFG1_ADLPC(1) | ADC_CFG1_ADIV(0) | ADC_CFG1_ADLSMP(1) | ADC_CFG1_MODE(1) | ADC_CFG1_ADICLK(0);

ADC0_CFG2 = 0x00000000 = ADC_CFG2_ADLSTS(0);

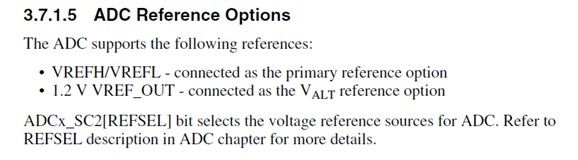

ADC0_SC2 = 0x00000001 = ADC_SC2_REFSEL(1) | ADC_SC2_ADTRG(0);

ADC0_SC3 = 0x00000000 = ADC_SC3_ADCO(0) | ADC_SC3_AVG(0);

Regarding VREF, there is something strange.

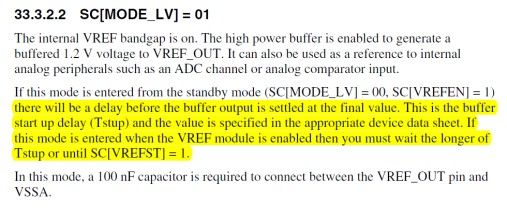

In the reference manual, it’s written:

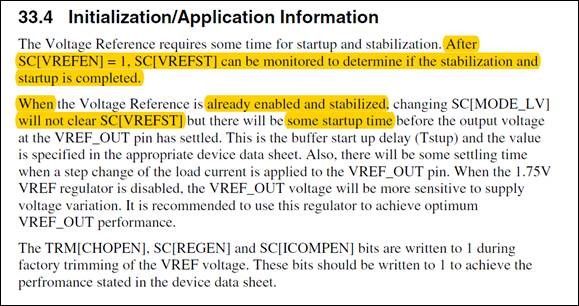

In the datasheet, tstup is given for a maximum of 100µs.

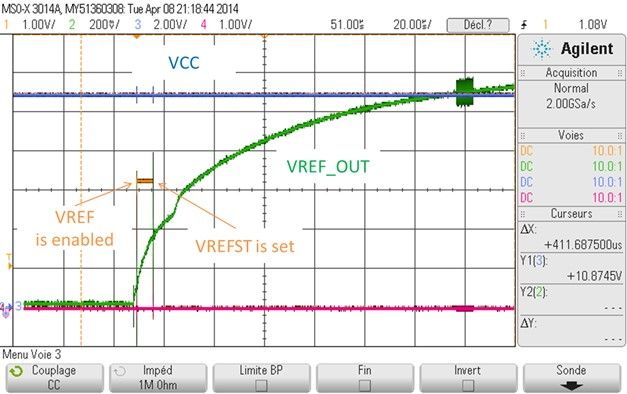

As you can see it on the following screenshot, VREFST flag takes about 6µs to be set (after VREF startup) and VREF_OUT takes more than tstup (100µs) to be stable.

So, we wonder why VREF_OUT takes more than 100µs to be stable and if it may have a link with our calibration issue.

In the reference manual, it is written that ADC used VREF_OUT as reference and not internal bandgap voltage.

So, if we start ADC calibration just after VREFST is set, VREF_OUT is still not stable and calibration is done with a reference that is not stable.

On some other PCBA, calibration works well whereas VREF_OUT has the same behavior.

Can you help us to understand these issues ?

Thanks in advance,

BR,

Philippe

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

According to calibration procedure: it looks like (it can also depends from application to application) for your type of application it will be better to do calibration once at the beginning (the best is at 25C), may be repeat calibration procedure several times (20x) and get the average values which will be stored in FLASH memory. And copy these values after each reset from flash to the ADC calibration registers.

regards

R.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Any feedback ?

BR,

Philippe

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

There are a couple of things that need corrected here.

1) There must be a 100nF capacitor on the VREF_OUT pin. Having 50nF by means of the two 100nF capacitors in series is not allowed.

2) There would appear to be some information missing from the reference manual and data sheet regarding the settling time when chop oscillator s being used (and it must be used to achieve the data sheet performance):

"When the chop oscillator is enabled, the settling time of the internal bandgap reference is defined by Tchop_osc_stup

(chop oscillator start up time). You must wait this time (Tchop_osc_stup) after the internal bandgap has been enabled to ensure the VREF internal reference voltage has stabilized."

The Tchop_osc_stup is defined to be a maximum value of 35ms.

I would ask that you remove one of the 100nF capacitors so that the resulting capacitance seen be the VREF_OUT pin is 100nF and then add a 35mS delay between configuring the VREF module and calibrating the ADC. I would expect this will resolve the variation in the calibration result.

I will look into getting the required changes made to the documentation.

Regards,

Alistair

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

After performing several tests, it appears that changing cap value does not change the calibration results.

The only good results are obtained if we wait for Tstup (100µs) when VREFEN is set.

But according to the RM this Tstup delay is only needed when VREFEN is set and only when switching from one MODE_LV mode to another one:

Can you confirm this, as it appears from our tests that setting VREF_SC = 0xE1 (meaning set VREFEN and MODE_LV=1 simultanously) we also need to wait for Tstup to get correct results.

BR,

Philippe.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello

According to the Kinetis design, can this capacitor be the root cause of the calibration issue ?

In fact, we wonder if we can keep these two capacitors without any side-effects. Can you tell us what are the potential side effects ?

Moreover, if we remove one 100nF, the settling time will be increase as well.

Best Regards,

Philippe

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Philippe,

Do you use the capacitor with SMT(surface mountable package) or insertion package? if you use insertion package, you can connect a float wire on the two capacitor pins on the bottom PCB side. If you use capacitor with SMT, you can remove one capacitor and connect float wire on the pins of capacitor.

If you remove one 100nF cap, as V(t)=1.2*(1-EXP(-t/RC)), C increases, |1/RC| decreases, the setting time will increase.

Hope it can help you.

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I can understand that capacitor need time to be charged, but measurements have shown that 100µs is not enough to fully charge this capacitor. The response time (at 5%) is around 250µs. Is it enough to wait 100µs ?

Moreover, in the reference manual, it is not mentioned to wait Tstup when the VREF enable switch from 0 to 1.

According to RM, I understand that Tstup must only be waited when VREF is already enabled and mode is changed.

Note as well that the capacitor on VREF_OUT is not 100nF as mentioned in the RM but 2x100nF in series = 50nF.

For the first designs we only had one 100nF. Is there a link with our issue ?

Best Regards,

Philippe

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

can you remove one 100nF capacitor so taht the cap is 100nF and have a try. I recommend you use the spec of capacitor defined in data sheet for the capacitor spec.

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

You use 1.2V VREF_OUT output voltage as the ADC reference voltage, because the VREF_OUT have to be connected to a 0.1uF capacitor, the VREF circuit has to charge the capacitor, the voltage of the Vref_out is rising based on the formula V(t)=1.2V*(1-EXP(-t/RC)), so time is required to charge the capacitor.

If you use the 1.2V Vref_out pin as ADC voltage reference, you should wait 100us as you said so that the transient process is ended, Vref_out voltage is stable, then you can do ADC calibration and have ADC sample.

Hope it can help you

BR

Xiangjun rong