- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: Handling NMI on bootup

Handling NMI on bootup

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Handling NMI on bootup

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi XingChang,

For one of the projects, we are using MKW36 chip, In which NMI pin used as wakeup source, so in FOPT we enabled NMI.

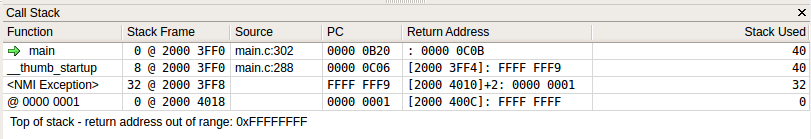

On reset, while booting, NMI is triggered and always enters into NMI handler. When looked into call stack it is observed that there is an NMI exception from where NMI handler is invoked.

In this scenario, the reset handler (_thumb_startup) is invoked two times. How to handle this situation? Can you please help us in understanding the code execution flow in this scenario.

As per the Reference manual, when NMI is active low processor executes an Exception entry and reads address of NMI handler from Vector table offset 8, and begins execution at NMI interrupt handler. But the call stack given below looks different and the PC value for NMI Exception shows 0xFFFFFFF9, this call stack is captured from J-Link debugger.

Thanks

Naven

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Install an NMI handler in Flash to catch the event out of reset by disabling NMI MUX function on the PIN.

Eg. from uTasker project

static void irq_NMI(void)

{

// this is executed immediately out of reset if the NMI line is enabled and held low

_CONFIG_PORT_INPUT_FAST_LOW(B, PORTB_BIT18, PORT_PS_UP_ENABLE); // set the NMI line to an input to remove the NMI function and allow the processor to continue

}

When you want to use the NMI during normal operation install a new handler in SRAM and reconfigure the pin MUX.

Eg. from uTasker project

// Allow the user to enter an NMI handler, ensuring that the NMI pin is configured as NMI function

// - note that the NMI must not have been disabled to allow this to work

//

extern void fnEnterNMI(void (*_NMI_handler)(void))

{

VECTOR_TABLE *ptrVect = (VECTOR_TABLE *)(RAM_START_ADDRESS);

ptrVect->ptrNMI = _NMI_handler; // enter interrupt handler

_CONFIG_PERIPHERAL(B, 18, (PB_18_NMI | PORT_PS_UP_ENABLE)); // set the NMI pin function

}

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark,

Thanks for the quick response.

NMI handler is already defined and is invoked on bootup, in handler the NMI pin is configured to other alternate function, there are no repeated NMI interrupts observed.

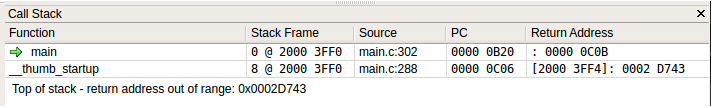

There is an observation, the reset handler (_thumb_start) is invoked twice. As per my understanding reset handler should be called only once.

During debugging I added a breakpoint in main function which is invoked from reset handler, here is the call stack once after entry into reset handler

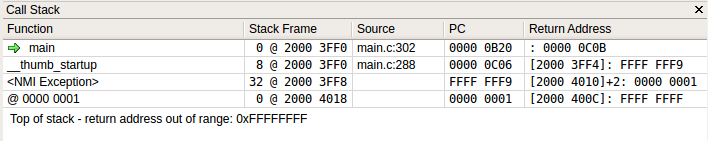

When I give run, the next call stack shows as given below, the control returned back to main again.

In first call stack frame, the 'NMI Exception' PC address shows as 0xFFFFFFF9, Is it valid address? As per my understanding, the PC address in call stack for this should show the NMI handler address (vector table offset 8). Is it because handler invoked before initialization complete?

Thanks

Naven

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Naven

Since the NMI interrupt will be taken immediately out of reset it may not be that easy to clearly see what happens with the debugger. Basically it sounds as though it is working as it should.

The 0xfffffff9 is the EXC_RETURN value - see Cortex Interrupt documentation for details - and this post: https://community.arm.com/developer/ip-products/processors/f/cortex-m-forum/4557/cortex-m4-exception...

Regards

Mark