- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: HELP!!! Last bit of Kinetis DSPI Byte Transfer is Trucated

HELP!!! Last bit of Kinetis DSPI Byte Transfer is Trucated

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have also put this question on the SDK forum, but I need to get a reply ASAP on this issue.

I'm struggling with trying to get SD Cards working with the K22F and I'm wondering about the dspi clock.

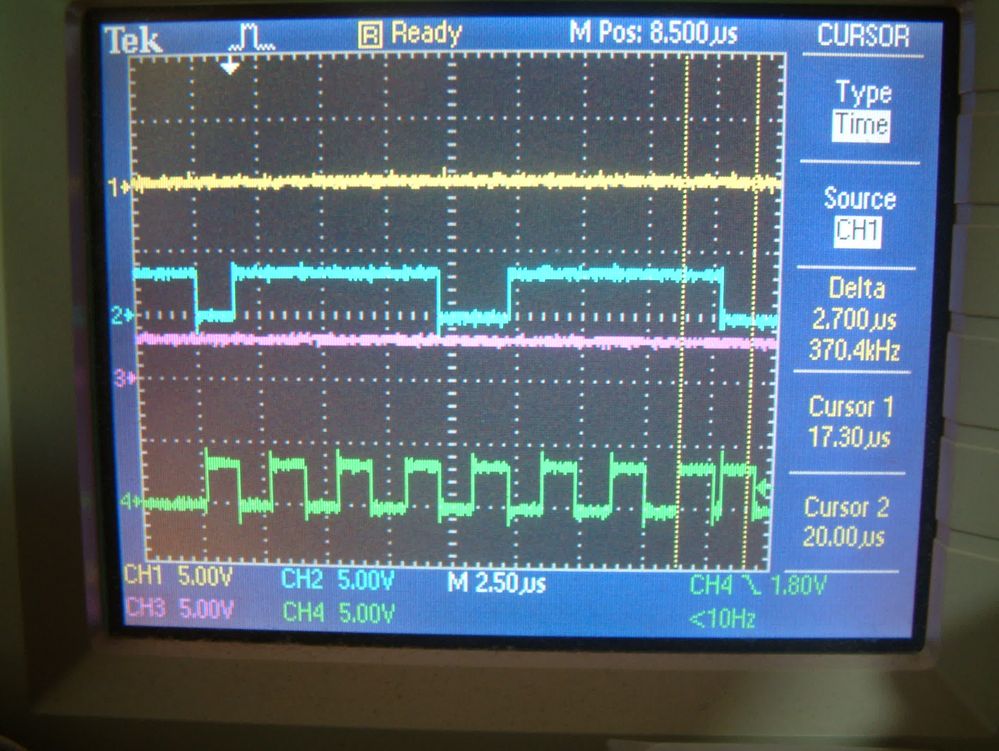

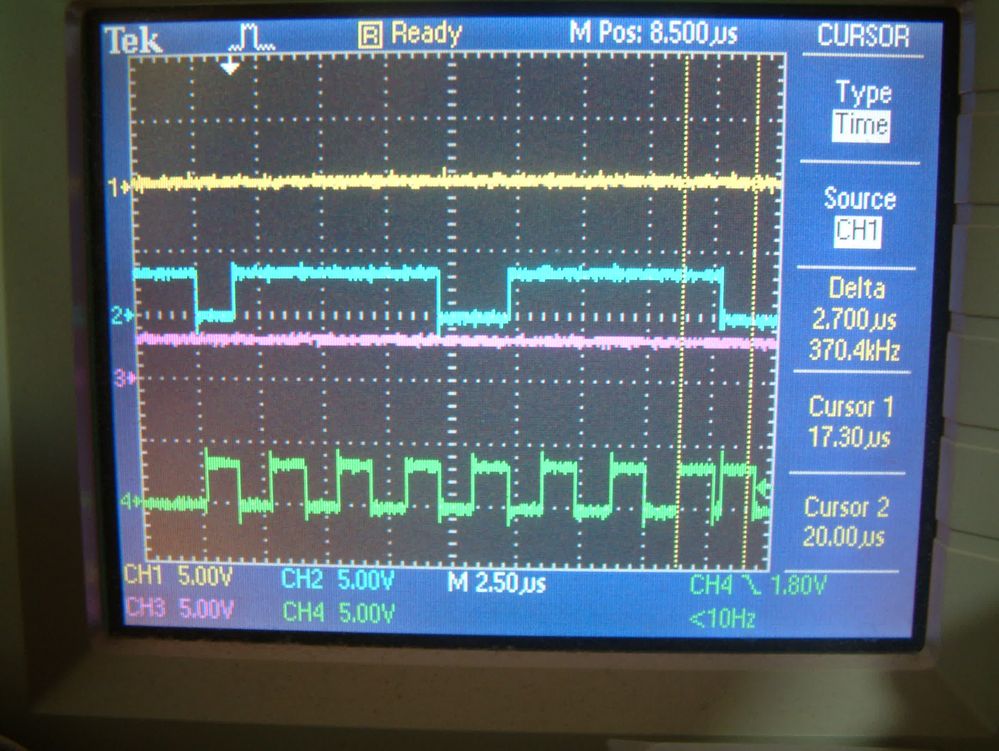

As I mentioned in a previous question, the last bit of a dspi byte transfer is truncated as you can see in this quick and dirty screenshot:

The bottom line is the dspi sck and you can see that the "low" half of the cycle is truncated into the first bit of the next transfer.

The dspi was selected from PE with a clock speed of 375kHz with Clock cfg.4 on a FRDM-k22F board.

I'm looking around and can't find any reason of what I'm doing wrong, 375kHz is a "Possible setting" so I presume that means that the clock is divided evenly (although evidence suggests this is not the case).

Can anybody help?

Thanx,

myke

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

It appears you need to add some time before starting the next SPI frame, this is done in the CTAR register through the PCSSCK and CSSCK fields. That way you can make sure the clock period isn't too short. Just had to fix this myself on a K10.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Myke

it reminds a similar problem that i had with KL15.

I have not the code on this PC,and i'm not shure at all that the situations are related.

I wrote my own routine for transmitting n bytes ,accessing directly to SPI register ,i had to use a GPIO pin as SPI CS,because that SPI (SPI0)was not able to keep CS costantly low during transfer of multiple bytes,and this was requested by the external peripheral.The original CS pin was left free.

At first attempts,after copied the last byte in the data register i checked SPI1_S & SPI_S_SPTEF_MASK ,but doing that is simply check that the output buffer is free, once it has moved the byte in the output shift register,but the transmission on pin could be still running,

the code at that point was faster than the shifting mechanism,so i issued another transmission too early,and thelast byte was truncated.

The workaround that i did was ,once the last byte was launched ,to check the original CS pin level as it was a GPIO:

while(!(GPIOD_PDIR & 0x10));

because differently than SPTEF ,the CS pin goes inactive only when all the bits are physically shifted out on pin.

Probaly it was not the better way to do what i needed,but this is the only thing that i can remember that could have something to do with your problem

Good luck

Diego

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Diego,

Could I see your code? I'm curious to see if it avoids the truncated bit issue that I started with as well as the spike shown in the 'scope shot above.

I do use a GPIO for !CS for the same reasons that you point out above. BUT, I monitor the output of the bytes before continuing by using the code:

for (wordsTransferred = 0; (kStatus_DSPI_Busy == DSPI_DRV_MasterGetTransferStatus(DSPI_MASTER_INSTANCE, &wordsTransferred)) ||

(wordsToTransfer != wordsTransferred);) {

}

As I found that "kStatus_DSPI_Busy" was being returned BEFORE the last byte had been sent.

Thanx,

myke

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Mark..sorry but i have no way to have the code.I can't acced to that PC

Furthermore i dont know no more how to attach files.Something looks changed.

Sorry

Diego

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Sorry,i missed your request.Lot of time is passed but today i'll try to find the codeit (is not in this PC)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

If it helps, I'm using the CONT and EOQ bits in the PUSHR register to make sure the /CS signal stays asserted when transferring multiple bytes, I haven't seen the data line glitches that Myke is seeing. Also, If you're using a polling routine to check for byte transmission, poll on the RFDF flag. Even if you're not receiving bytes, polling on that would guarantee that the byte is transmitted AND one is received. Read the POPR register and write to the RFDF bit to clear before transmitting the next byte.

I believe the KL spi module is the same as the one on the KE part; I had to use GPIO to control /CS as well. It's not as sophisticated as the K10/K20 spi module where you can tell it there are more bytes to transfer.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

It appears you need to add some time before starting the next SPI frame, this is done in the CTAR register through the PCSSCK and CSSCK fields. That way you can make sure the clock period isn't too short. Just had to fix this myself on a K10.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi David,

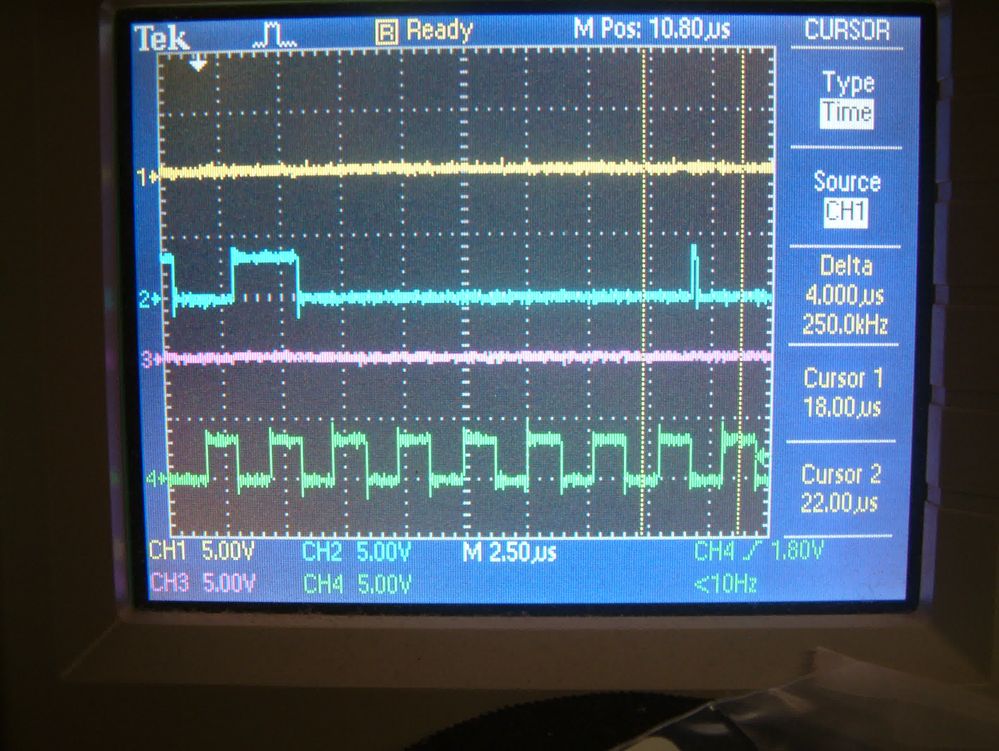

Thank you for the pointer - I was able to get the final clock looking pretty good:

A couple of things:

- To dynamically read & change the bits of CSSCK & PCSSCK, I found: http://mcuoneclipse.com/2014/05/29/how-to-add-register-details-view-in-eclipse/ which is a plugin & patch that allows register bits to be manipulated from KDS (Eclipse). I believe CW had/has this capability but it's nice to have it on KDS.

- If you look at the waveform above, you'll see the data spikes at the end of the 8th clock cycle high. Is there any way to remove that? (It's the purist in me.)

Thanx!

myke