- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Flexbus problem

Flexbus problem

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Flexbus problem

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

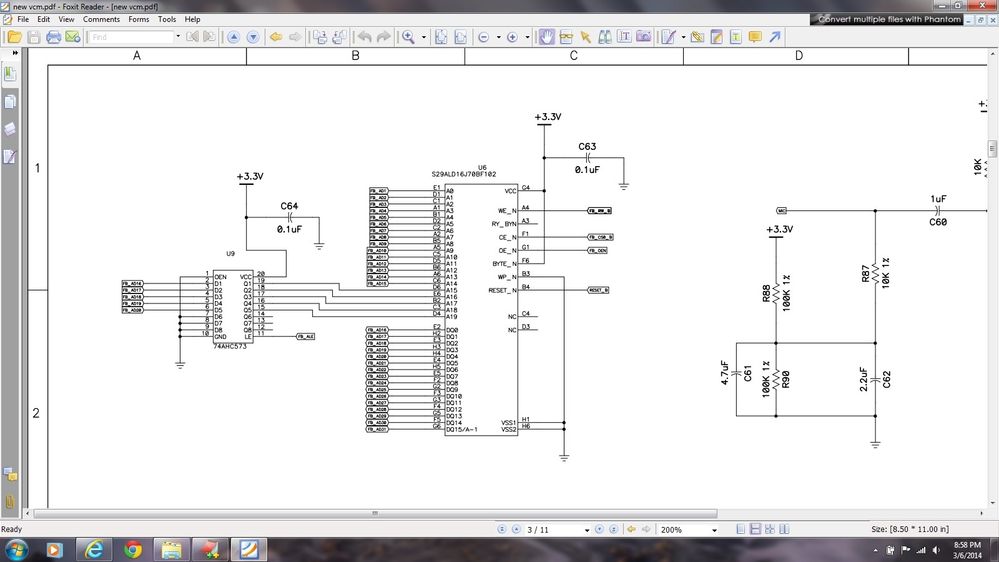

I have a custom board using a MK10FN1M0VLQ12. I have a 512K 16 bit Flash connected to the Flexbus. When I try to access the flash I get the following error "Target request failed: ARM GDI Protocol Adapter: Stop failed. non fatal error.". What would cause this error? I am using a P&E multi-link bdm. Also I have the K10 address 1 connected to Address 0 of the flash for 16 bit access. Is this correct?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Dennis,

Would you please provide details on that issue? For example, the schematics of flexbus connection, the code to initialize the flexbus, and which instruction causing the issue you mentioned? Thanks for your patience!!

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kan,

/***********************************************************************

*

* Function: FlexBus_Init

*

* Purpose:

* configure the flex bus to access external flash

*

* Processing:

* clears all ring attributes.

*

* Parameters:

* ring: ring buffer id

*

* Outputs: None

*

* Returns: None

*

* Notes: None

*

**********************************************************************/

void Flexbus_Init(void)

{

SIM_SCGC7 |= SIM_SCGC7_FLEXBUS_MASK; // Enable the clock to the FlexBus module

FB_CSAR0 = (uint32)&EX_FLASH_START_ADDRESS; // 0x60000000

FB_CSCR0 = FB_CSCR_PS(2) // 16-bit port

// | FB_CSCR_AA_MASK // auto-acknowledge

// | FB_CSCR_EXTS_MASK // ALE asserted thoughtout cycle

// | FB_CSCR_ASET(0x1) // assert chip select on second clock edge after address is asserted

// | FB_CSCR_WS(0x1) // 1 wait state - may need a wait state depending on the bus speed

// | FB_CSCR_BEM_MASK // Byte enable enabled

;

FB_CSMR0 = FB_CSMR_BAM(7) //Set base address mask for 2M address space

| FB_CSMR_V_MASK //Enable cs signal

;

//enable BE signals - note, not used in this example

// FB_CSPMCR = 0x02200000;

//fb clock divider 3

// SIM_CLKDIV1 |= SIM_CLKDIV1_OUTDIV3(0x3);

// configure external pins

PORTD_PCR6 = PORT_PCR_MUX(5); // address/data 0

PORTD_PCR5 = PORT_PCR_MUX(5); // address/data 1

PORTD_PCR4 = PORT_PCR_MUX(5); // address/data 2

PORTD_PCR3 = PORT_PCR_MUX(5); // address/data 3

PORTD_PCR2 = PORT_PCR_MUX(5); // address/data 4

PORTC_PCR10 = PORT_PCR_MUX(5); // address/data 5

PORTC_PCR9 = PORT_PCR_MUX(5); // address/data 6

PORTC_PCR8 = PORT_PCR_MUX(5); // address/data 7

PORTC_PCR7 = PORT_PCR_MUX(5); // address/data 8

PORTC_PCR6 = PORT_PCR_MUX(5); // address/data 9

PORTC_PCR5 = PORT_PCR_MUX(5); // address/data 10

PORTC_PCR4 = PORT_PCR_MUX(5); // address/data 11

PORTC_PCR2 = PORT_PCR_MUX(5); // address/data 12

PORTC_PCR1 = PORT_PCR_MUX(5); // address/data 13

PORTC_PCR0 = PORT_PCR_MUX(5); // address/data 14

PORTB_PCR18 = PORT_PCR_MUX(5); // address/data 15

PORTB_PCR17 = PORT_PCR_MUX(5); // address/data 16

PORTB_PCR16 = PORT_PCR_MUX(5); // address/data 17

PORTB_PCR11 = PORT_PCR_MUX(5); // address/data 18

PORTB_PCR10 = PORT_PCR_MUX(5); // address/data 19

PORTB_PCR9 = PORT_PCR_MUX(5); // address/data 20

PORTB_PCR8 = PORT_PCR_MUX(5); // address/data 21

PORTB_PCR7 = PORT_PCR_MUX(5); // address/data 22

PORTB_PCR6 = PORT_PCR_MUX(5); // address/data 23

PORTA_PCR29 = PORT_PCR_MUX(5); // address/data 24

PORTA_PCR28 = PORT_PCR_MUX(5); // address/data 25

PORTA_PCR27 = PORT_PCR_MUX(5); // address/data 26

PORTA_PCR26 = PORT_PCR_MUX(5); // address/data 27

PORTA_PCR25 = PORT_PCR_MUX(5); // address/data 28

PORTA_PCR24 = PORT_PCR_MUX(5); // address/data 29

PORTB_PCR21 = PORT_PCR_MUX(5); // address/data 30

PORTB_PCR20 = PORT_PCR_MUX(5); // address/data 31

PORTB_PCR19 = PORT_PCR_MUX(5); // OEN

PORTC_PCR11 = PORT_PCR_MUX(5); // R/W

PORTD_PCR0 = PORT_PCR_MUX(5); // ALE

PORTD_PCR1 = PORT_PCR_MUX(5); // CS

}

Kan the issue is cause when I try to read location 0x60000000.

Thank-you for the reply.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Dennis,

It looks like you comment out AA bit configuration.

| FB_CSCR0 = FB_CSCR_PS(2) | // 16-bit port | |

| // | | FB_CSCR_AA_MASK | // auto-acknowledge |

| // | | FB_CSCR_EXTS_MASK // ALE asserted thoughtout cycle | |

| // | | FB_CSCR_ASET(0x1) // assert chip select on second clock edge after address is asserted | |

| // | | FB_CSCR_WS(0x1) | // 1 wait state - may need a wait state depending on the bus speed |

| // | | FB_CSCR_BEM_MASK // Byte enable enabled |

and I didnt see the FB_TA is connecting with the external flash device, so that would cause problem during read operation as bus hangs during a transfer. Please enable this bit and try again.

Thanks for your patience!!

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kan,

Thank-you for the Reply. I am not getting an error, but when I do a 16 bit I get back 0xC0FF when it should be 0xFFFF.

Thank-you

Dennis Essenmacher

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Dennis,

Did you change the Flexbus_Init()? If yes, please post it here for a review. Thanks for your patience!

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kan,

void Flexbus_Init(void)

{

SIM_SCGC7 |= SIM_SCGC7_FLEXBUS_MASK; // Enable the clock to the FlexBus module

FB_CSAR0 = (uint32)&EX_FLASH_START_ADDRESS; // 0x60000000

FB_CSCR0 = FB_CSCR_PS(3) // 16-bit port

| FB_CSCR_AA_MASK // auto-acknowledge

// | FB_CSCR_EXTS_MASK // ALE asserted thoughtout cycle

| FB_CSCR_ASET(0x1) // assert chip select on second clock edge after address is asserted

| FB_CSCR_WS(0x3) // 1 wait state - may need a wait state depending on the bus speed

| FB_CSCR_RDAH(1)

// | FB_CSCR_BEM_MASK // Byte enable enabled

;

FB_CSMR0 = FB_CSMR_BAM(7) //Set base address mask for 2M address space

| FB_CSMR_V_MASK //Enable cs signal

;

//enable BE signals - note, not used in this example

// FB_CSPMCR = 0x02200000;

//fb clock divider 3

// SIM_CLKDIV1 |= SIM_CLKDIV1_OUTDIV3(0x3);

// configure external pins

// PORTD_PCR6 = PORT_PCR_MUX(5); // address/data 0

PORTD_PCR5 = PORT_PCR_MUX(5); // address/data 1

PORTD_PCR4 = PORT_PCR_MUX(5); // address/data 2

PORTD_PCR3 = PORT_PCR_MUX(5); // address/data 3

PORTD_PCR2 = PORT_PCR_MUX(5); // address/data 4

PORTC_PCR10 = PORT_PCR_MUX(5); // address/data 5

PORTC_PCR9 = PORT_PCR_MUX(5); // address/data 6

PORTC_PCR8 = PORT_PCR_MUX(5); // address/data 7

PORTC_PCR7 = PORT_PCR_MUX(5); // address/data 8

PORTC_PCR6 = PORT_PCR_MUX(5); // address/data 9

PORTC_PCR5 = PORT_PCR_MUX(5); // address/data 10

PORTC_PCR4 = PORT_PCR_MUX(5); // address/data 11

PORTC_PCR2 = PORT_PCR_MUX(5); // address/data 12

PORTC_PCR1 = PORT_PCR_MUX(5); // address/data 13

PORTC_PCR0 = PORT_PCR_MUX(5); // address/data 14

PORTB_PCR18 = PORT_PCR_MUX(5); // address/data 15

PORTB_PCR17 = PORT_PCR_MUX(5); // address/data 16

PORTB_PCR16 = PORT_PCR_MUX(5); // address/data 17

PORTB_PCR11 = PORT_PCR_MUX(5); // address/data 18

PORTB_PCR10 = PORT_PCR_MUX(5); // address/data 19

PORTB_PCR9 = PORT_PCR_MUX(5); // address/data 20

PORTB_PCR8 = PORT_PCR_MUX(5); // address/data 21

PORTB_PCR7 = PORT_PCR_MUX(5); // address/data 22

PORTB_PCR6 = PORT_PCR_MUX(5); // address/data 23

PORTA_PCR29 = PORT_PCR_MUX(5); // address/data 24

PORTA_PCR28 = PORT_PCR_MUX(5); // address/data 25

PORTA_PCR27 = PORT_PCR_MUX(5); // address/data 26

PORTA_PCR26 = PORT_PCR_MUX(5); // address/data 27

PORTA_PCR25 = PORT_PCR_MUX(5); // address/data 28

PORTA_PCR24 = PORT_PCR_MUX(5); // address/data 29

PORTB_PCR21 = PORT_PCR_MUX(5); // address/data 30

PORTB_PCR20 = PORT_PCR_MUX(5); // address/data 31

PORTB_PCR19 = PORT_PCR_MUX(5); // OEN

PORTC_PCR11 = PORT_PCR_MUX(5); // R/W

PORTD_PCR0 = PORT_PCR_MUX(5); // ALE

PORTD_PCR1 = PORT_PCR_MUX(5); // CS

}

Thank-you for the reply.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Dennis,

I think it should be a timing issue, please try use | FB_CSCR_ASET(0x3) instead to see if it makes any difference.

Please kindly let me know if the problem is still there.

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I am getting this same error on Kinetis_MK20DX256VLL7_msd_mfs_generic_host (from USB 4.1.1 stack ) when I am in debug mode and I press "stop" on the project. I am using CodeWarrior 10.6, Windows XP. I am using the TWR-K20D72M.

Any updates on this? Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Robert,

I found some code issue in that project, in khci_kinetis.c, you will find a definition for bdt like following:

/* Global variables */

#define _BDT_RESERVED_SECTION_

#if(defined _BDT_RESERVED_SECTION_)

#ifdef __CWCC__

#pragma define_section usb_bdt ".usb_bdt" RW

__declspec(usb_bdt) uint_8 uint_8_ptr bdt;

You have to change it as below:

/* Global variables */

#define _BDT_RESERVED_SECTION_

#if(defined _BDT_RESERVED_SECTION_)

#ifdef __CWCC__

#pragma define_section usb_bdt ".usb_bdt" RW

__declspec(usb_bdt) uint_8 bdt[512];//uint_8_ptr bdt;

With this modification, you can make it run as expected, and the following is the test result at my end. Please kindly refer to it for more details.

FAT demo

Waiting for USB mass storage to be attached...

Mass Storage Device Attached

******************************************************************************

* FATfs DEMO *

* Configuration: LNF Enabled, Code page =1258 *

******************************************************************************

******************************************************************************

* DRIVER OPERATION *

******************************************************************************

1. Demo function: f_mount

Initializing logical drive 0...

Initialization complete

-----------------------------------------------------------------------------

2. Demo functions:f_getfree, f_opendir, f_readdir

getting drive 0 attributes...............

Logical drive 0 attributes:

FAT type = FAT16

Bytes/Cluster = 2048

Number of FATs = 2

Root DIR entries = 512

Sectors/FAT = 250

Number of clusters = 63858

FAT start (lba) = 36

DIR start (lba,clustor) = 536

Data start (lba) = 568

...

127716 KB total disk space.

127624 KB available.

-----------------------------------------------------------------------------

******************************************************************************

* DRECTORY OPERATION *

******************************************************************************

1. Demo functions:f_opendir, f_readdir

Directory listing...

----A 2014/04/16 17:25 32253 tek00000.png

----A 2014/04/16 17:34 31451 tek00001.png

----A 2014/07/04 14:57 20549 tek00002.png

DR--- 2010/12/25 23:30 0 DIRECT~1

D---- 2010/01/01 00:00 0 DIRECT~2

3 File(s), 84253 bytes total

2 Dir(s)

-----------------------------------------------------------------------------

2. Demo functions:f_mkdir

2.0. Create <Directory_1>

2.1. Create <Directory_2>

2.2. Create <Sub1> as a sub directory of <Directory_1>

2.3. Directory list

Directory listing...

----A 2014/04/16 17:25 32253 tek00000.png

----A 2014/04/16 17:34 31451 tek00001.png

----A 2014/07/04 14:57 20549 tek00002.png

DR--- 2010/12/25 23:30 0 DIRECT~1

D---- 2010/01/01 00:00 0 DIRECT~2

3 File(s), 84253 bytes total

2 Dir(s)

-----------------------------------------------------------------------------

3. Demo functions:f_getcwd, f_chdir

3.0. Get the current directory

CWD: 0:/

3.1. Change current directory to <Directory_1>

3.2. Directory listing

Directory listing...

D---- 2010/01/01 00:00 0 .

D---- 2010/01/01 00:00 0 ..

D---- 2010/01/01 00:00 0 sub1

0 File(s), 0 bytes total

3 Dir(s)

3.3. Get the current directory

CWD: 0:/Directory_1

-----------------------------------------------------------------------------

4. Demo functions:f_stat(File status), f_chmod, f_utime

4.1. Get directory information of <Directory_1>

DR--- 2010/12/25 23:30 0 Directory_1

4.2 Change the timestamp of Directory_1 to 12.25.2010: 23h 30' 20

4.3. Set Read Only Attribute to Directory_1

4.4. Get directory information (Directory_1)

DR--- 2010/12/25 23:30 0 Directory_1

-----------------------------------------------------------------------------

5. Demo functions:f_rename

Rename <sub1> to <sub1_renamed> and move it to <Directory_2>

Directory listing...

D---- 2010/01/01 00:00 0 .

D---- 2010/01/01 00:00 0 ..

D---A 2010/01/01 00:00 0 SUB1_R~1

0 File(s), 0 bytes total

3 Dir(s)

-----------------------------------------------------------------------------

6. Demo functions:f_unlink

Delete Directory_1/sub1_renamed

Directory listing...

D---- 2010/01/01 00:00 0 .

D---- 2010/01/01 00:00 0 ..

0 File(s), 0 bytes total

2 Dir(s)

******************************************************************************

* FILE OPERATION *

******************************************************************************

1. Demo functions:f_open,f_write, f_printf, f_putc, f_puts, fclose

1.0. Create new file <New_File_1> (f_open)

File size = 0

1.1. Write data to <New_File_1>(f_write)

1.2. Flush cached data

File size = 52

1.3. Write data to <New_File_1> (f_printf)

1.4. Flush cached data

File size = 103

1.5. Write data to <New_File_1> (f_puts)

1.6. Flush cached data

File size = 152

1.7. Write data to <New_File_1> uses f_putc function

1.8. Flush cached data

File size = 199

1.9. Close file <New_File_1>

-----------------------------------------------------------------------------

2. Demo functions:f_open,f_read, f_seek, f_gets, f_close

2.0. Open <New_File_1> to read (f_open)

2.1. Get a string from file (f_gets)

Line 1: Write data to file uses f_write function

2.2. Get the rest of file content (f_read)

Line 2: Write data to file uses f_printf function

Line 3: Write data to file uses f_puts function

Line 4: Write data to file uses f_putc functionûöF¬

â•:7Rz}™ yzjw8 ¸×áÀ—»ÃÐ ¹òÍ

ä‹Hïk¨Wã½c' ²7këÞÑ%VrC×»Ô¼ÒSÈÑèR+NjD¡¾òû>ú3‰SËþo ^ÎI Pë±ñ‰þ/Directory_1

2.3. Close file (f_close)

-----------------------------------------------------------------------------

3. Demo functions:f_stat, f_utime, f_chmod

3.1. Get information of <New_File_1> file (f_stat)

----A 2010/01/01 00:00 199 New_File_1.dat

3.2 Change the timestamp of Directory_1 to 12.25.2010: 23h 30' 20 (f_utime)

3.3. Set Read Only Attribute to <New_File_1> (f_chmod)

3.4. Get directory information of <New_File_1> (f_stat)

-R--A 2010/12/25 23:30 199 New_File_1.dat

3.5. Clear Read Only Attribute of <New_File_1> (f_chmod)

3.6. Get directory information of <New_File_1>

----A 2010/12/25 23:30 199 New_File_1.dat

-----------------------------------------------------------------------------

4. Demo functions:f_ulink

Rename <New_File_1.dat> to <File_Renamed.txt>

Directory listing...

D---- 2010/01/01 00:00 0 .

D---- 2010/01/01 00:00 0 ..

----A 2010/12/25 23:30 199 FILE_R~1.TXT

1 File(s), 199 bytes total

2 Dir(s)

-----------------------------------------------------------------------------

5. Demo functions:f_truncate

Truncate file <File_Renamed.txt>

5.0. Open <File_Renamed.txt> to write

5.1. Seek file pointer

Current file pointer: 0

File pointer after seeking: 102

5.2. Truncate file

File size = 102

5.3. Close file

-----------------------------------------------------------------------------

6. Demo functions:f_forward

6.0. Open <File_Renamed.txt> to read

6.1. Forward file to terminal

Line 1: Write data to file uses f_write function

Line 2: Write data to file uses f_printf function

6.2. Close file

-----------------------------------------------------------------------------

7. Demo functions:f_ulink

Delete <File_Renamed.txt>

Directory listing...

D---- 2010/01/01 00:00 0 .

D---- 2010/01/01 00:00 0 ..

0 File(s), 0 bytes total

2 Dir(s)

*------------------------------ DEMO COMPLETED ------------------------ *

******************************************************************************

Hope that helps,

Have a great day,

B.R

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Robert,

Actually I run the CW project well without meeting such issue, but I found it generates hard fault when it tried to send out the setup packet, maybe that is the issue you met. I will continue to debug and let you know when I have any progress.

Have a great day,

B.R

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------