- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Re: FTM - updating modulus value

FTM - updating modulus value

FTM - updating modulus value

I have a board design which incorporates a GPS receiver as a precision timing reference. The receiver produces a pulse at the start of each GPS second which is then followed by serial data which includes time and date. In my application code, I've configured a GPIO for input capture and see an interrupt on an FTM channel at each rising edge of the pulse from the receiver. I've also configured the same FTM to generate a timer overflow interrupt nominally once per millisecond. The interrupt handler updates the system time at each TOF interrupt, with the once per second pulse from the GPS receiver used to maintain long-term accuracy by compensating for oscillator error.

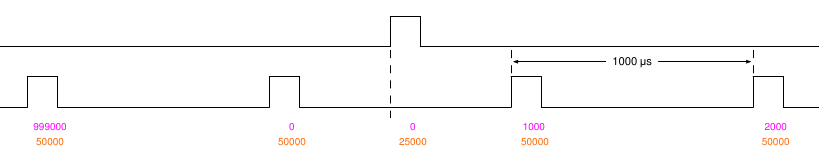

My algorithm design requires a 500 us offset between the 1 PPS signal and the internal clock in order to achieve +/-1/2 LSB timing accuracy. Ideal timing at the end of one GPS second and the start of the next is illustrated in the diagram below, where the top trace represents the 1 PPS signal from the GPS receiver and the lower trace TOF interrupts. Values in magenta represent time within the second in microseconds, while the numbers in orange below are cycle count values between events, i.e., FTMx -> MOD + 1. The FTM is configured for 50 MHz system bus clock value, prescale divide = 1.

Again, this is the ideal case. In practice, the last TOF interrupt before the input capture (1 PPS) event at the end of a GPS second may vary in time by as much as 20 us when the GPS is locked.

Quoting section xx.3.5 of the FTM section in the users manual,

"Writing to the MOD register latches the value into a buffer. The MOD register is updated

with the value of its write buffer according to Registers updated from write buffers.

If FTMEN = 0, this write coherency mechanism may be manually reset by writing to the

SC register whether BDM is active or not."

The manual reset capability described in the second paragraph is needed in order to change the modulus value in the input capture interrupt handler, as I essentially need to restart the internal time base at each 1 PPS event, with an initial delay value of 500 us (25000 system clock cycles). Despite the information provided about resetting the coherency mechanism, I've not found a way to make that work in practice. I've tried each of the following sequences. (Apologies for the formatting -- I see an icon for source code, but it appears to want to reformat my entire post and I didn't find any examples to show how a source code block should be included in the new user information.)

#define MODULUS_SYSTIMER_INITIAL 24999

/*

* Restart system timer, sequence 1

*/

FTM0 -> CNT = 0;

FTM0 -> MOD = MODULUS_SYSTIMER_INITIAL;

FTM0 -> SC != 1 << FTM_SC_TOIE_SHIFT;

/*

* Restart system timer, sequence 2

*/

FTM0 -> CNT = 0;

FTM0 -> SC != 1 << FTM_SC_TOIE_SHIFT;

FTM0 -> MOD = MODULUS_SYSTIMER_INITIAL;

/*

* Restart system timer, sequence 3

*/

FTM0 -> SC != 1 << FTM_SC_TOIE_SHIFT;

FTM0 -> CNT = 0;

FTM0 -> MOD = MODULUS_SYSTIMER_INITIAL;

/*

* Restart system timer, sequence 4

*/

FTM0 -> CNT = 0;

FTM0 -> SC &= ~(1 << FTM_SC_TOIE_SHIFT);

FTM0 -> MOD = MODULUS_SYSTIMER_INITIAL;

FTM0 -> SC |= 1 << FTM_SC_TOIE_SHIFT;

Implementing any of the sequences shown within the the input capture interrupt handler, I consistently see the first TOF interrupt occur 1000 us after the 1 PPS pulse. (As a diagnostic, I drive separate GPIOs high for the duration of each interrupt handler. Maximum time to service either TOF or input capture interrupts is 3.4 us, so there is ample idle time between events.)

It occurs to me that perhaps the problem is that the COUNT value is not being reset to zero as expected, even though the documentation claims that any write to FTMx -> CNT updates its value to that stored in CNTIN. As a final note, I'm using only the PTM functions, so TMEN and CNTIN are never altered from their reset values of zero.

If it's possible to restart the TOF timer as I need, I'm clearly not understanding the sequence of events needed to do so. If the documentation is in fact accurate, an example showing how to restart the timer as it appears possible would be most appreciated.

Hello J Stark

Thank you for your reply, the MK22DX128VLF5 and MK22FN128VLH10 FTM modules are similar that we can say they're the same.

When the FTM is reset, this means that the chip also was reset so it has to pass again with the startup sequence. The FTM module needs to be configured again to work as you desire.

It is important to confirm that the CNTIN value is the one you desire. When you write CNT with no zero value the counter will start from the CNTIN value.

When the FTM clock is initially selected, by writing a non-zero value to the CLKS bits,

the FTM counter starts with the value 0x0000.

Let me know if this is helpful, if you have more questions do not hesitate to ask me.

Best regards,

Omar

In my application, CNTIN is always zero, so a write to COUNT which restarts the counter at zero is exactly what I need. What I've not been able to get to work as expected is reset of the modulo coherency mechanism so that I can restart the timer within the current TOF interval when the input capture event occurs.

Since my application should never see both TOF and input capture interrupts at the same time, I've restructured my code to simply disable then re-enable the FTM each time an input capture event occurs. Before writing the clock select bits, I set the modulus to generate the first TOF interrupt at 500 us, then after selecting the bus clock to start the timer I update the modulus value to generate subsequent TOF interrupts at 1 ms intervals until the next input capture event. This strategy has proven to be effective in my application, however would not be suitable if any other interrupts could be generated by the FTM while the input capture event is being serviced.

Hello J Stark

Thank you for your interest in NXP Semiconductor products and the opportunity to serve you.

It would be helpful if you provide me the part number you're working with.

Best regards,

Omar