- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: FEE CLOCK ERROR WITH FLL

FEE CLOCK ERROR WITH FLL

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

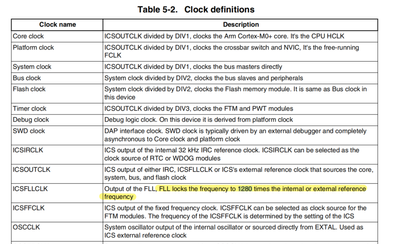

I am working with an MKE06Z128VQH4 microcontroller, and I am configuring the clock frequency in MCUXpresso. I want to use FEE mode because I have a 12 MHz crystal. My board is custom-made, and I’m having problems with the configuration — mainly with the FLL, which has a constant of 1280. That value multiplies the frequency and exceeds the limit, giving me an error, and I really don’t know how to modify that constant. I’m new to using MCUXpresso.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @Iotelctronic ,

Yes, I configure the setting with the config tools. My version is v25.06. However, I think you issue is not related to the config tools version.

Please be attention to the Frequency range when setting RDIV. You can click on RDIV in the clocks diagram on the left side of the screenshot to trigger the related settings on the right.

RDIV can range from 32 to 1024 only when you select the high-frequency range; otherwise, as you can see, its maximum value can only be set to 128.

Hope it helps.

BR

Celeste

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @Iotelctronic ,

Thanks for your post and sorry for the late response.

I have checked the Reference manual of MKE06Z128VQH4. You can see that the FLL is fixed at 1280. It cannot be modified in the Clock Config tool, which is expected and not an issue.

Additionally, please refer to Table 5-5, which lists all available combinations of sources from the OSC clock for this device. As shown, in FEE mode, considering the limitation that the FLL is fixed at 1280, we recommend using an 8–10 MHz OSC with RDIV set to 256, or a 16–20 MHz OSC with RDIV set to 512.

A 12 MHz OSC is not listed, which indicates it is not recommended. I tested both 10 MHz and 16 MHz configurations in the Clock Config Tools, and there were no issues.

Hope it helps.

BR

Celeste

-------------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the "ACCEPT AS SOLUTION" button. Thank you!

-------------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for responding. I changed the crystal to 8 MHz because I'm actually using 8 MHz as shown in the evaluation board schematic. I was confused due to a previous project with another NXP MCU that I was working on.

However, even after configuring it for 8 MHz to use FEE mode, I get an error because the RDIV divider only goes up to 128. If I divide by 128, I get an FLL of 80 MHz, which exceeds the limit. Yet, I see in the information you sent that it can be divided up to 512.

Did you configure the settings manually, or did you use the Config Tool? If you used the Config Tool, which version are you using?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @Iotelctronic ,

Yes, I configure the setting with the config tools. My version is v25.06. However, I think you issue is not related to the config tools version.

Please be attention to the Frequency range when setting RDIV. You can click on RDIV in the clocks diagram on the left side of the screenshot to trigger the related settings on the right.

RDIV can range from 32 to 1024 only when you select the high-frequency range; otherwise, as you can see, its maximum value can only be set to 128.

Hope it helps.

BR

Celeste

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello, I set up the clock correctly as you told me in the MCUXpresso tool and it worked well, thank you very much.