- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Core Clock divide

Core Clock divide

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Core Clock divide

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I've got strange problem using SIM_CLKDIV1 to lower core clock on K80

I'm running PLL on this board and i want to be able to divide high PLL clocks to not exceed bus/core clocks limits.

The problem is if i use this:

SIM -> CLKDIV1 = (SIM_CLKDIV1_OUTDIV1(0)| //core

SIM_CLKDIV1_OUTDIV2(1)| // Busclk

SIM_CLKDIV1_OUTDIV3(3)| // FlexBus

SIM_CLKDIV1_OUTDIV4(7)); // Flash

It works, every clock is divided properly but if i try:

SIM -> CLKDIV1 = (SIM_CLKDIV1_OUTDIV1(1)| //core

SIM_CLKDIV1_OUTDIV2(1)| // Busclk

SIM_CLKDIV1_OUTDIV3(3)| // FlexBus

SIM_CLKDIV1_OUTDIV4(7)); // Flash

Write is ignored and i end up with default values. Where is the catch? I read that maximum divide ratio between core and other clocks is 8 but i'm not exceeding this limitations

Thanks for any help :smileyhappy:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

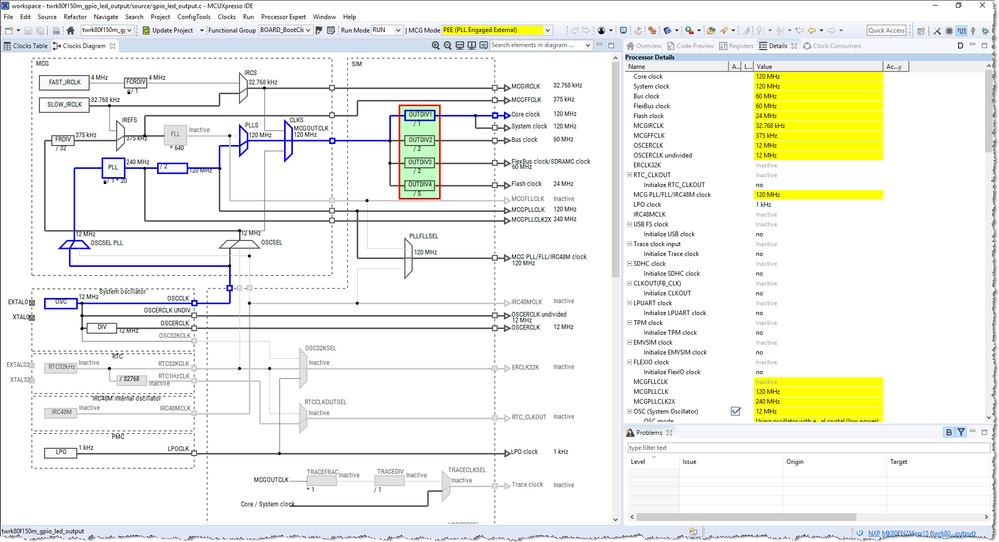

I am using Clocks tool of MCUXpresso IDE, the GPIO example is able to run after modify the divider.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

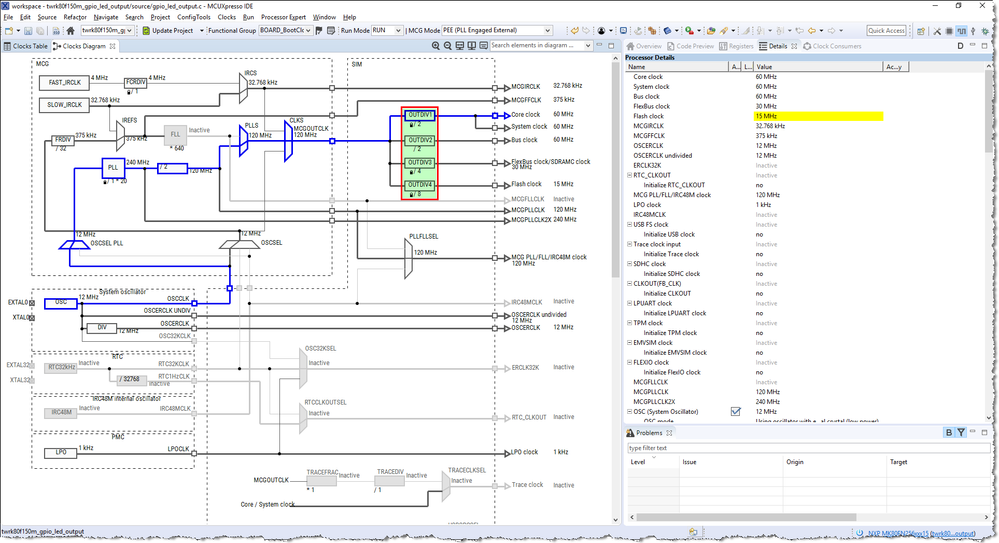

That's really usefull feature in MCUXpresso and now i'm able to set SIM_CLKDIV1 correctly but i noticed that's not perfect.

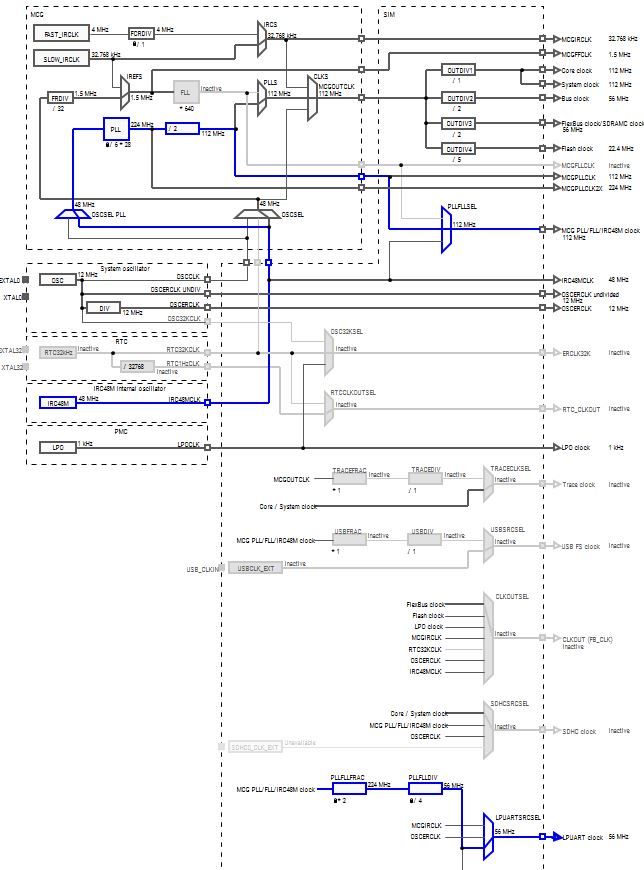

Not sure if it's bug or i'm doing something wrong but if i want to clock my UART using this tool it's not working properly, wrong clock is selected.

How it's setuped:

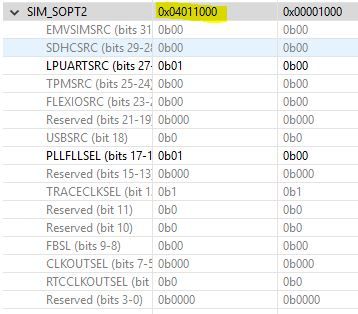

Register values in clocks tab :

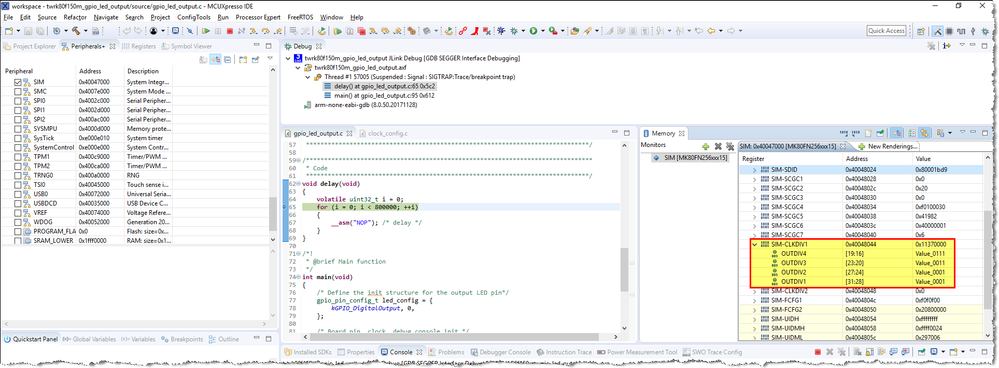

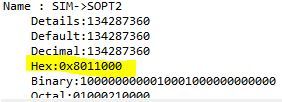

What i get after i run the code:

And the problem is not only when i want to use PLL to feed UART, it always end up with OSCERCLK clock.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

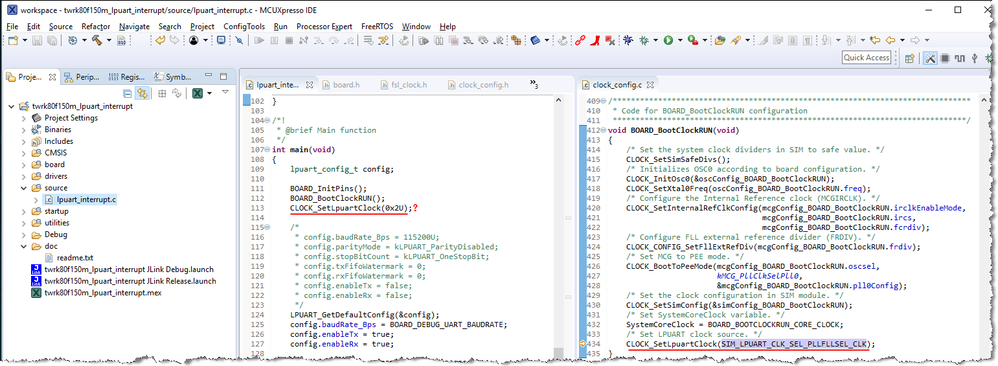

Please check if there is someplace else select the clock of LPUART again.

For example: the lpuart_interrupt will select OSCERCLK after BOARD_BootClockRUN

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------