- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: Clock configuration problem

Clock configuration problem

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Clock configuration problem

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

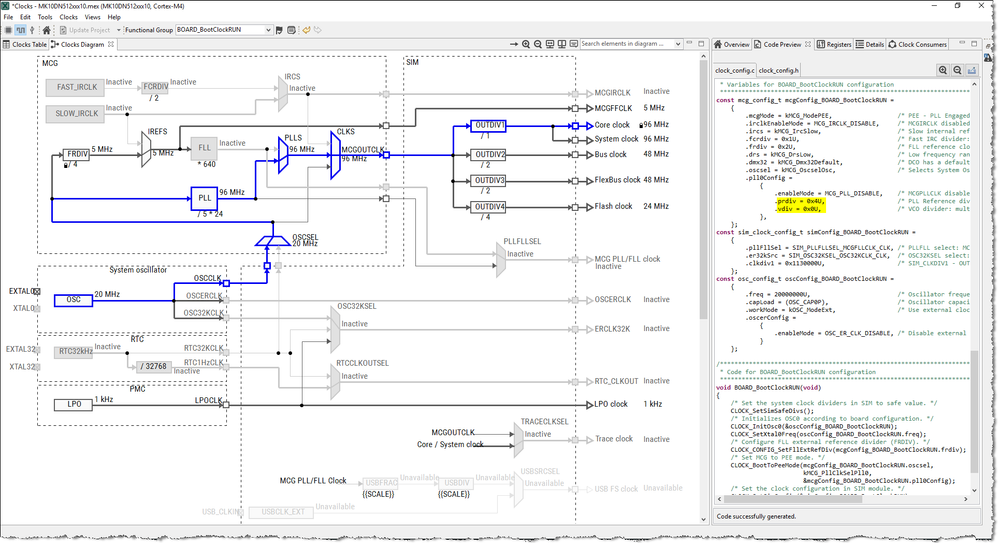

First I set the parameters

const mcg_config_t mcgConfig_BOARD_BootClockRUN =

{

.mcgMode = kMCG_ModePEE, /* PEE - PLL Engaged External */

.irclkEnableMode = kMCG_IrclkEnable, /* MCGIRCLK enabled, MCGIRCLK disabled in STOP mode */

.ircs = kMCG_IrcSlow, /* Slow internal reference clock selected */

.fcrdiv = 0x0U, /* Fast IRC divider: divided by 1 */

.frdiv = 0x0U, /* FLL reference clock divider: divided by 32 */

.drs = kMCG_DrsLow, /* Low frequency range */

.dmx32 = kMCG_Dmx32Default, /* DCO has a default range of 25% */

.oscsel = kMCG_OscselOsc, /* Selects System Oscillator (OSCCLK) */

.pll0Config =

{

.enableMode = MCG_PLL_DISABLE, /* MCGPLLCLK disabled */

.prdiv = 0x2U, /* PLL Reference divider: divided by 25 */

.vdiv = 0x20U, /* VCO divider: multiplied by 48 */

//.prdiv = 0x18U, /* PLL Reference divider: divided by 25 */

//.vdiv = 0x18U, /* VCO divider: multiplied by 48 */

},

};

const sim_clock_config_t simConfig_BOARD_BootClockRUN =

{

.pllFllSel = SIM_PLLFLLSEL_MCGPLLCLK_CLK, /* PLLFLL select: MCGPLLCLK clock */

.er32kSrc = SIM_OSC32KSEL_RTC32KCLK_CLK, /* OSC32KSEL select: RTC32KCLK clock (32.768kHz) */

.clkdiv1 = 0x01130000U, /* SIM_CLKDIV1 - OUTDIV1: /1, OUTDIV2: /2, OUTDIV3: /2, OUTDIV4: /4 */

};

const osc_config_t oscConfig_BOARD_BootClockRUN =

{

.freq = 20000000U, /* Oscillator frequency: 50000000Hz */

.capLoad = (OSC_CAP0P), /* Oscillator capacity load: 0pF */

.workMode = kOSC_ModeExt, /* Use external clock */

.oscerConfig =

{

.enableMode = kOSC_ErClkEnable, /* Enable external reference clock, disable external reference clock in STOP mode */

}

};

My external clock is 20000000 so I set prdiv = 0x2U and vdiv = 0x20U in order to get PLL = 100000000 (maximum system clock for MK10DN512)

And prescalers clkdiv1 = 0x01130000U to get SYS_CLK = PLL and BUS_CLK = PLL/2

Then I use the library function

void BOARD_BootClockRUN(void)

{

/* Set the system clock dividers in SIM to safe value. */

CLOCK_SetSimSafeDivs();

/* Initializes OSC0 according to board configuration. */

CLOCK_InitOsc0(&oscConfig_BOARD_BootClockRUN);

CLOCK_SetXtal0Freq(oscConfig_BOARD_BootClockRUN.freq);

/* Configure FLL external reference divider (FRDIV). */

CLOCK_CONFIG_SetFllExtRefDiv(mcgConfig_BOARD_BootClockRUN.frdiv);

/* Set MCG to PEE mode. */

CLOCK_BootToPeeMode(mcgConfig_BOARD_BootClockRUN.oscsel,

kMCG_PllClkSelPll0,

&mcgConfig_BOARD_BootClockRUN.pll0Config);

/* Configure the Internal Reference clock (MCGIRCLK). */

CLOCK_SetInternalRefClkConfig(mcgConfig_BOARD_BootClockRUN.irclkEnableMode,

mcgConfig_BOARD_BootClockRUN.ircs,

mcgConfig_BOARD_BootClockRUN.fcrdiv);

/* Set the clock configuration in SIM module. */

CLOCK_SetSimConfig(&simConfig_BOARD_BootClockRUN);

/* Set SystemCoreClock variable. */

//SystemCoreClock = BOARD_BOOTCLOCKRUN_CORE_CLOCK;

SystemCoreClock = CLOCK_GetFreq(SYS_CLK);

BusClock = CLOCK_GetFreq(BUS_CLK);

}

It stacks at function CLOCK_SetPbeMode on

while ((MCG->S & (MCG_S_IREFST_MASK | MCG_S_CLKST_MASK)) !=

(MCG_S_IREFST(kMCG_FllSrcExternal) | MCG_S_CLKST(kMCG_ClkOutStatExt)))

{

}

How can I configure clocks?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The problem was prdiv = 0x2U and vdiv = 0x20U - it's not absolute values - it bits in registers.

now SYS_CLK = 96000000 BUS_CLK = 48000000

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Evgeny Erenburg,

The MCUXpresso Clock Tools will generate these codes by itself after you configure the corresponding clock.

You don't need to manually modify these codes.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------