- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: Clarification of operation of PDB DAC Triggers

Clarification of operation of PDB DAC Triggers

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

In the reference manual for K22F (MK22FN512VLH12,- K22P64M120SF5V2RM) the detailed description of the PDB DAC output triggers appears to be missing.

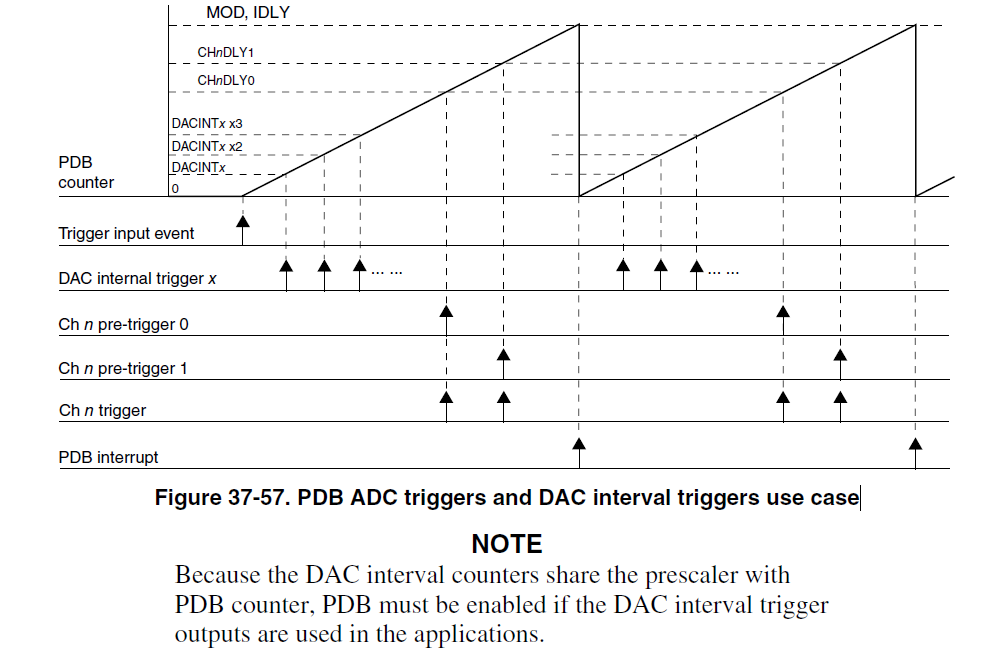

Referring to a similar K22F chip (MK22FN1M0AVLH12 - K22P64M120SF5V2RM) there is a detailed description in section 37.4.3 including a diagram showing timing of DACINTx outputs (Figure 37-57).

The description and timing diagram along with the block diagram Figure 37-1 clearly indicates that the DACINT triggers are based on a separate counter. There is quite a lot of Freescale documentation that describes the PDB DACINT triggers as a comparison value against the main PDB counter rather than as a separate counter.

The difference is quite significant.

Does this vary between Kinetis devices?

In any case, my main question relates to the DACINT counter when the PDB is operated in free-running mode after a software trigger.

Quoting from the K22P64M120SF5V2RM manual (since this is missing from the actual manual for the chip being used): 37.4.3 DAC interval trigger outputs

...

"DAC interval counters are also reset when the PDB counter reaches the MOD register value; therefore, when the PDB counter rolls over to zero, the DAC interval counters starts anew."

When experimenting with the the PDB triggering and a DAC it appears that the DACINT counter is NOT reset when the main PDB counter rolls over. It is only reset when a trigger occurs. This seems consistent with the Block diagram Figure 37-1. This means that effectively in free-running mode the DACINT trigger is unrelated to the the main PDB counter after the initial trigger. This limits the usefulness somewhat.

Tests done:

- PDB set up to have a period of 10us, DACINT set to a period of 12us. I would expect no DAC conversions. The DAC changes occur at a period of 12us after the software trigger. The PDB period appears to have no effect.

- PDB set up to have a period of 10us, DACINT set to a period of 6us. I would expect 1 DAC conversion every 10us with the first 6us after the trigger. The DAC changes occur at a period of 6us after the software trigger. The PDB period appears to have no effect.

Using single-shot mode with a relatively slow PIT channel as a trigger gives the expected results confirming that the DACINT counter is reset when triggered.

- 100 us PIT period, 10 us PDB period, 3 us DACINT value. There is a group of three DAC changes at a 3us interval every 100 us.

I would appreciate confirmation or argument about my conclusion.

Thanks

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Pgo,

Thank you for the code and message.

You are right, the Fig 38-1 is correct, there is independent DAC interval counter, which can count the tick, the tick is the same as driving the PDB counter.

All the Kinetis family PFB modules are similar.

I will report the documentation ambiguous part to documentation team so that they can update.

Thank you for pointing the doc issue.

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, PGO

Regarding your question that the PDB triggers ADC, I confirm that there is NOT so-called separate counter for DAC, there is only ONE PDB0_DACINT0 register for MK22FX512AVLH12, MK22FN1M0AVLH12.

The DAC sampling frequency is only determined by the PDB0_MOD register, as you know that when the PDB0_CNT reach up to the PDB0_DACINT0 register, an internal trigger to DAC will be generated, if the DACTRGSEL bit in DAC0_C0 reg is cleared so the hardware trigger is selected, the DAC pin output voltage is updated immediately.

Pls refer to the screenshot.

Hope it can help you

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi XiangJun Rong,

Thanks for your reply but it can't be correct!

The figure you posted (and was quoted by me!) clearly shows the single DACINTx value producing multiple DAC internal triggers - the third line of the figure. These occur at multiples of the DACINTx value (DACINTx x1, x2 etc).

I have confirmed this occurs - I stated this in my question. This is inconsistent with the DACINT being compared with the main PDB counter. So the DAC sampling frequency is not determined by the PDB period unless the DACINT period is greater than 50% of the PDB counter value and an external trigger is used.

The block diagram from K22P121M120SF7RM shows a separate DAC interval counter with a reset signal coming from a comparator. This appears to be a counter that runs from [0..DACINTx]. The operation of this circuit is consistent with the behaviour I have seen.

Please reconcile this with your description.

Incidentally my original question is mostly about the incorrect description about when the DACINTx counter is reset - not its existence.

bye

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, PGO,

I have to admit that the description of DAC interval counter is confusing and inconsistent in the RM, what we are arguing is whether there is DAC interval counter, if it exists, what is the driving clock source.

It is helpful if you can post your code here which can prove that the "DAC interval counter" does exist, with which I can test on my tower board.

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi XiangJun,

Attached are three programs tested on a MK22FN512VLH12:

- Simple example. Sets up the PDB for Free-running mode with software trigger, PDB period = 1ms, DACINT period 20us. The output waveform confirms that the DAC changes at 20 us interval irrespective of the PDB period i.e. the DAC output period is not (directly) related to the PDB counter period.

- A more complicated example. The PDB is operating in one-shot mode hardware triggered by a PIT at 1 ms interval. The PDB period is set to 170 us, the DAC interval to 20 us. This means that the DAC will be triggered 8 times for each trigger of the PDB. The output waveform confirms that the DAC changes in groups of 8 steps at 20 us spacing every 1 ms. This is again consistent with the DAC being a separate counter that is enabled when the PDB counter is running and reset by the same trigger as the PDB counter.

- Similar to the first example but PDB period = 100us, DACINT period 30us. This produces a stepped waveform similar to 1 but it illustrates that the DAC counter is NOT being reset when the PDB counter is rolling over in free-running mode. The spacing of the DAC outputs should have a discontinuity every 3 steps.

The above is consistent with the timing diagram provided in some manuals but inconsistent with some training material and the text description in the same manuals.

These examples happen to use a MULT and PRESCALE value of 0 but I can confirm that changing these does affect the DACINT period confirming that the DAC counter is clocked by the same divided clock as the main PDB counter. It would not be sensible to do otherwise.

So - are all the PDBs in Kinetis devices similar?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Pgo,

Thank you for the code and message.

You are right, the Fig 38-1 is correct, there is independent DAC interval counter, which can count the tick, the tick is the same as driving the PDB counter.

All the Kinetis family PFB modules are similar.

I will report the documentation ambiguous part to documentation team so that they can update.

Thank you for pointing the doc issue.

BR

Xiangjun Rong