- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: Bus fault when reading CnSC register from FTM1 channel 2 on MKV46

Bus fault when reading CnSC register from FTM1 channel 2 on MKV46

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Bus fault when reading CnSC register from FTM1 channel 2 on MKV46

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

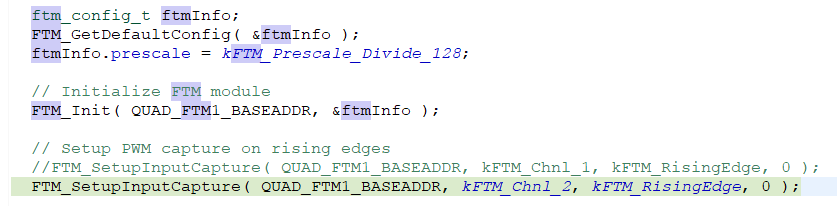

I am using the NXP libraries to configure FTM1 on an MKV46F256VLL16 - but am getting a bus fault upon calling FTM_SetupInputCapture. This appears to occur during the read to the CnSC register for channel 2. Other registers and channels of the same FTM module are not affected. FTM_SetupInputCapture is called after FTM_Init, which enables the clock gates to the module. Note that the debugger is stopped due to a bus fault at FTM_SetupInputCapture below:

Inside FTM_SetupInputCapture:

The bus fault is marked as precise, and the BFAR is set to the address of FTM1 channel 2 CnSC, indicating that this is the access that caused the fault. Note that if the other FTM_SetupInputCapture line above was not commented out, the fault would still only occur when configuring the second channel.

My understanding is that reads of the CnSC register should be valid as long as the clock gate for FTM1 is enabled. I have also tried enabling the clock gate as shown below, and then reading the register - which also results in the same fault. This is done with interrupts disabled to eliminate the possibility of outside interference in the time domain. Any memory protection features remain at their default settings.

Any advice on how to address this issue would be much appreciated

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I believe I have found the problem... FTM1 channel 2 does not actually exist on this device. The datasheet shows that FTM1 has only two channels, 0 and 1:

The datasheet appears to cover all parts the reference manual covers - which seems to mean that the reference manual refers to registers that don't actually exist in any of the hardware.

Datasheet:

It's also worth noting that the pin configuration tool in MCUXpresso allows for configuring the I/O capture / control pin for FTM1 channel 2 - which is not documented in the datasheet - this creates further confusion about the (non) existence of FTM1 channel 2. My conclusion is that this part of the hardware does not exist - because it doesn't appear to actually work. It would be nice if the documentation would be updated to reflect that.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

As you mentioned, FTM1 only has 2 channels. You can see the number of channels for each FTM instance in Table 39-1. FTM Instantiations of the KV4x Reference Manual.

I'm reviewing the comments you mentioned about the pin configuration tool. Are you referring to ConfigTools? Could you share with me how you were performing the initialization in the tool?

Best Regards,

Pablo