- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: Buck peak current mode has no PWM deadtime

Buck peak current mode has no PWM deadtime

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Buck peak current mode has no PWM deadtime

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I’m trying to implement Peak Current Mode on a KIINETIS CPU (it’s a MKV46F256). Peak current mode uses a fixed duty which is cleared by the comparator when the peak current reaches the 6 bit DAC value. It’s explained in a bit more detail in App Note AN4485, section 3.1.7 Current-limit PWM. (its a different CPU but same eFlexPWM unit)

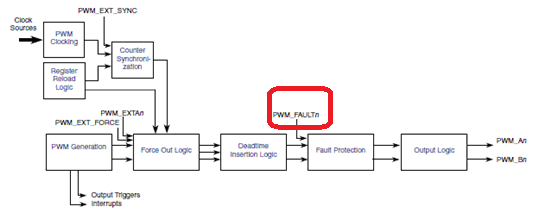

It’s suggests using the eFlex PWM fault inputs for the submodule

“where the comparator output will be used as the fault input of the PWM module”

Also this question "PWM termination using the analogue comparator" also states using the fault inputs.

"The CMP output signal can be as a fault signal, which can be connected to fault signal of eFlexPWM module via crossbar and disable PWM signal automatically."

But the fault inputs only take affect after the deadtime insertion logic.

This means when you implement a synchronous buck you will get shoot through on the FETs (e.g. they will both be on at for a small amount of time when they switch).

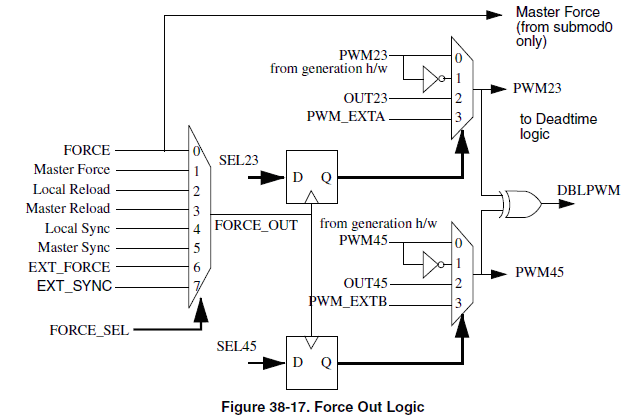

I think I might be able to use the Force Out logic and connect the comparator output to the EXT_SYNC to select OUT23 on it’s rising edge, e.g. turn off the PWM before the deadtime insertion logic.

But there is no automatic means of re-enabling the PWM23 output, e.g. changing SEL23 back to 0 and generating another FORCE_OUT clock.

Since this chip is marketed as a digital power supply chip and it states the following…

“This PWM module can generate various switching patterns, including highly sophisticated waveforms. It can be used to control all known Switched Mode Power Supplies (SMPS) topologies”

I’m guessing I must have missed something.

Any help in this matter would be greatly appreciated.

Chris

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Chris,

I see your dilemma, but I think you can use software to exchange PWM output setting. You can generate two interrupts with the local reloading and Fault interrupt events. In the local reloading ISR, you can change FORCE_SEL bits to select EXT_SYNC or EXT_FORCE so that external CMP output event can change the PWM output to OUTxx source when the EXT_SYNC signal is coming. In the Fault ISR(from CMP output signal), you can change FORCE_SEL bits to selec Local Reload so that the local reload event can change the PWM output to PWM23 source when the local reload event is coming.

This is my opinion, pls consider if it is feasible.

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi XiangJun,

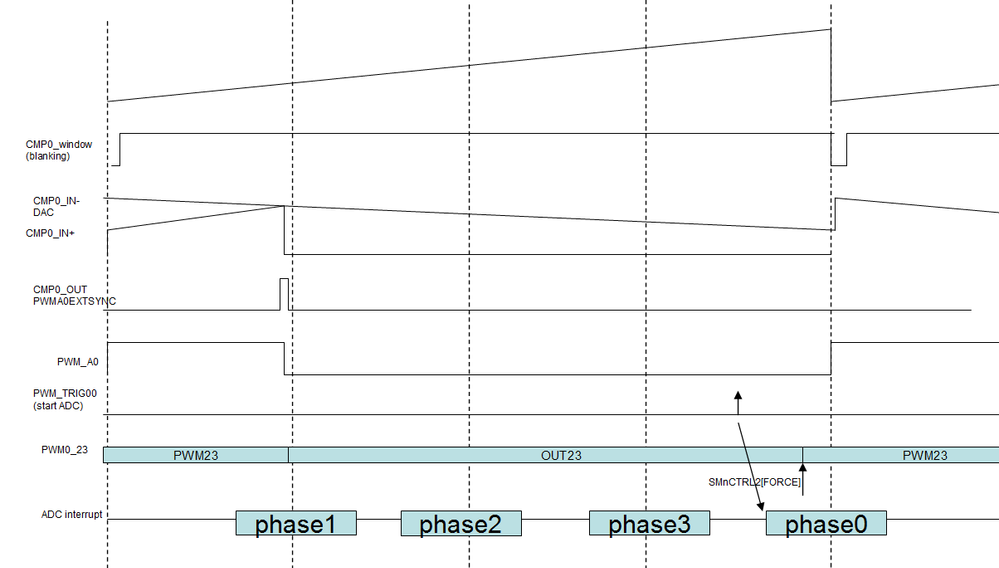

I was thinking of triggering my ADC sample near the end of the period (this helps with phase erosion) so my ADC interrupt would occur near the end of my period. FORCE_SEL would set to EXT_SYNC from the comparator output, then in my ADC interrupt I would

- set SEL23 to PWM23

- use SMnCTRL2[FORCE] to latch in PWM23

- set SEL23 to OUT23

Would this work? or do I need to mess around with FORCE_SEL?

This leaves the following problems

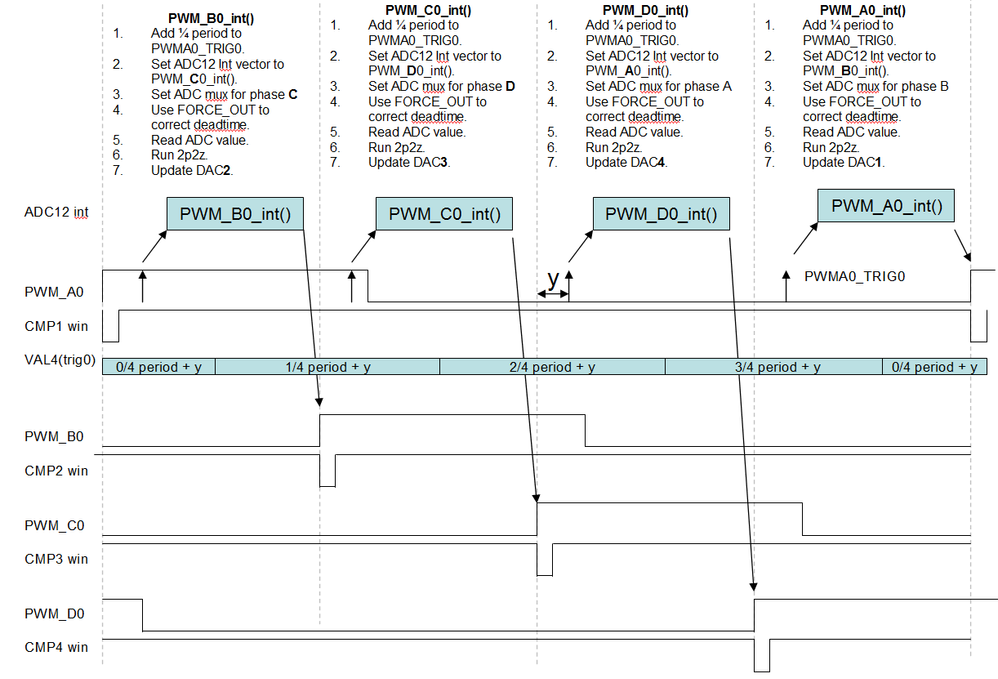

- I need to generate a 4 phase peak current mode controller

- Each buck will run at out of phase with each other

- Sample the ADC at 4 different points and call a different ADC interrupt.

- I need to generate 4 blanking windows, each one out of phase to each comparator

- I need slope compensation on each DAC output

I have 4 eFlexPWM submodules, so generating 4 PWMs is sorted. To make these out of phase I will have to adjust VAL2/3 to turn on/off at the correct time, eg

- PWM0_VAL2/3 -> 0=on 0+max duty=off

- PWM1_VAL2/3 -> 0+1/4 period = on, 0+1/4 period+max duty = off

- PWM2_VAL2/3 -> 0+2/4 period = on, 0+2/4 period+max duty = off

- PWM3_VAL2/3 -> 0+3/4 period = on, 0+3/4 period+max duty = off

On each ADC interrupt I would set the ADC trigger to be generated in the next 1/4 period and change the ADC inputs to sample my next buck Vout and to reset PWM23 from OUT23 on each submodule.. I'm happy with this.

I don't know how I can generate the 4 out of phase blanking windows ;-(

We only have two Programmable Delay blocks (PDB), so I can't use this to generate my windows. I can't use PWM_B to generate a window since it has no connection to the XBARA.

The only crazy idea I have come up with is to add a small RC filter to output pin PWM_A0 and feed this back in to the chip and use the XBARA to connect this to the comparator window signal. This isn't a great for a digital solution. Do you have any ideas?

I also need slope compensation on the 6 bit DAC. In the app note AN4485 it talks about using the 12 bit DAC which has some special feature to do this, but that's totally missing from the 6 bit DACs ;-(

Your help in this matter is greatly appreciated.

chris

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Chris,

Frankly speaking, I am not very clear about your idea. If you can draw a diagram which displays the required timing and ADC triggering point, it is fine.

Anyyway, it is okay to set the FORCE_SEL bits in PWMA_SMnCTRL2 as 3b'000(The local force signal, CTRL2[FORCE], from this submodule is used to force updates.), you can set the FORCE bit by software to switch the PWMx_A source anywhere.

Regarding the ADC triggering, If you hope that PWMA_A0/B0/C0/D0 can all trigger ADC, I think you can consider to route

PWMA0 Trigger 0,PWMA1 Trigger 0,PWMA2 Trigger 0,PWMA3 Trigger 0 to AOI via XBARB crossbar and do an OR logic, then use AOI output signal to trigger ADC12 module.

Hope it can help you

BR

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi XiangJun,

thank you for your reply.

I like the idea of ORing the PWMA triggers using the XBARB crossbar.

My plan was to only use PWMA0_Trigger0 to trigger the ADC, and on every interrupt adjust PWMA0_Trigger0 by ¼ period as shown below. Your way saves me a couple of instructions.

But my problems are still the same.

1) How can I generate 4 blanking windows (CMP1/2/3/4_win) for the comparators.

2) How can I add a slope to the DAC1/2/3/4 output for slope compensation.

Cheers

Chris