- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Design Studio

- :

- fsl_debug problem change frequency

fsl_debug problem change frequency

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

fsl_debug problem change frequency

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

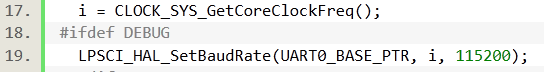

i'm using a kl46 with kds 3.1 and the sdk 1.3. I have a problem with this function where i change the frequency of my cpu according with some flag:

void CPU_Clock_Setting(void) { int i = 0; byte error = 0; DisableInterrupts; if (flag_lcd || flag_usb) {//se LCD on o USB inserita vado alla max freq error = CLOCK_SYS_UpdateConfiguration(0, kClockManagerPolicyForcible); i = CLOCK_SYS_GetCoreClockFreq(); #ifdef DEBUG LPSCI_HAL_SetBaudRate(UART0_BASE_PTR, i, 115200); #endif I2C0_SetClockConfiguration(); ADC_SetClockConfiguration(); } else{//altrimenti scendo alla configurazione di risparmio error = CLOCK_SYS_UpdateConfiguration(1, kClockManagerPolicyForcible); i = CLOCK_SYS_GetCoreClockFreq(); #ifdef DEBUG LPSCI_HAL_SetBaudRate(UART0_BASE_PTR, i, 115200); #endif I2C0_SetClockConfiguration(); ADC_SetClockConfiguration(); } EnableInterrupts; }

the problem is when the function CLOCK_SYS_UpdateConfiguration is called, when the fsl_debug enter in the function

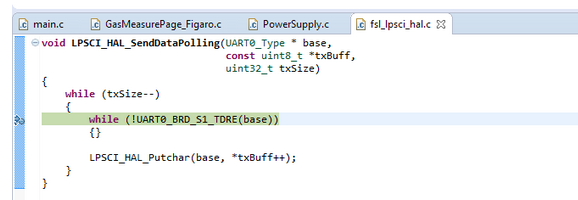

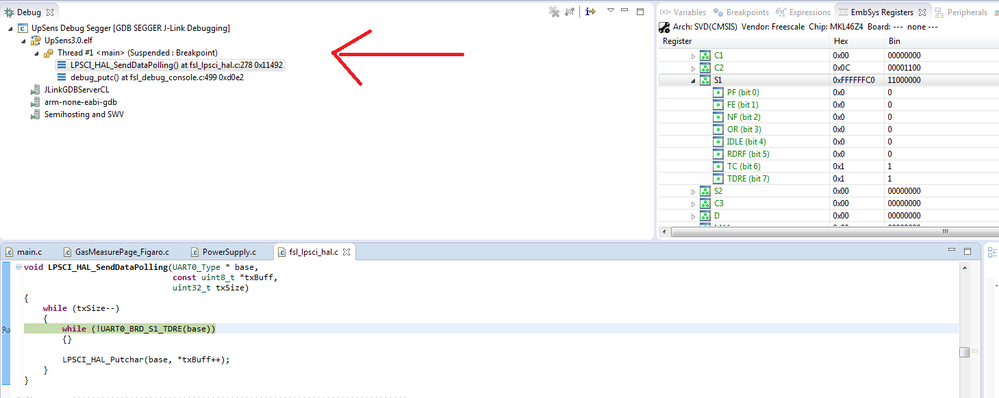

void LPSCI_HAL_SendDataPolling(UART0_Type * base, const uint8_t *txBuff, uint32_t txSize) { while (txSize--) { while (!UART0_BRD_S1_TDRE(base)) {} LPSCI_HAL_Putchar(base, *txBuff++); } }

it remain in the while loop. why this? i have add the function LPSCI_HAL_SetBaudRate for re-set the clock of the UART but same problem. Thanks

Configur

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alice,

yes but my problem is to pass from PLL to BLPE mode. In this mode the UART crash and there is no reason. Now i'm bored to try to find a solution (if there is....), i will use the PLL in all two configuration. The micro will consume more power ....

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

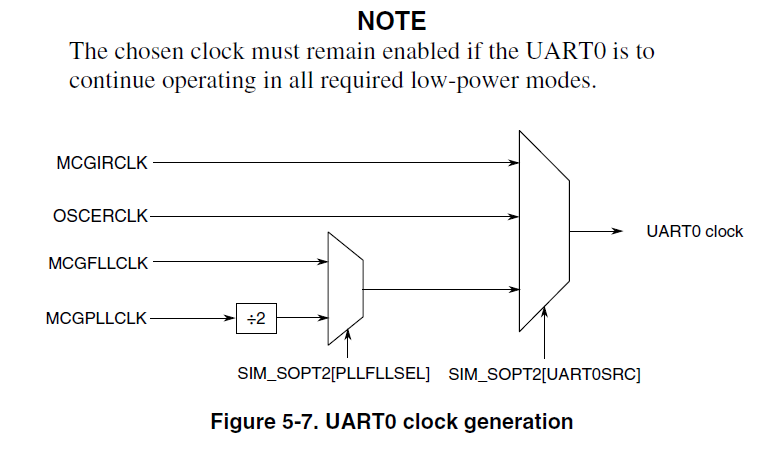

Hello Daniele,

The clock source of the UART0 not the CPU core clock , so there is some error :

And about configure the clock and the baud rate , i recommend you refer to the demo code under KSDK1.3:

\KSDK_1.3.0\examples\frdmkl46z\driver_examples\lpsci\lpsci_blocking\kds

in the initialize function , you can hwo to configure the clock source of UART and the baud rate :

// Initialize the lpsci module with base address and config structure

LPSCI_DRV_Init(BOARD_DEBUG_UART_INSTANCE, &lpsciState, &lpsciConfig);

Hope it helps

Have a great day,

Alice Yang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

i have tried to set the clock source of the lpsci to ESC source (i have a 16mhz oscillator)

when i call the function :

void CPU_Clock_Setting(void) {

int i = 0;

byte error = 0;

DisableInterrupts;

if (flag_lcd || flag_usb) {//se LCD on o USB inserita vado alla max freq

error = CLOCK_SYS_UpdateConfiguration(0, kClockManagerPolicyAgreement);

//CLOCK_SYS_SetConfiguration(&clockMan1_InitConfig0);

i = CLOCK_SYS_GetCoreClockFreq();

#ifdef DEBUG

//CLOCK_SYS_SetLpsciSrc(0, kClockLpsciSrcOsc0erClk);

//LPSCI_HAL_SetBaudRate(0, i, 115200);

//i = CLOCK_SYS_GetLpsciFreq(0);

#endif

I2C0_SetClockConfiguration();

ADC_SetClockConfiguration();

} else{//altrimenti scendo alla configurazione di risparmio

error = CLOCK_SYS_UpdateConfiguration(1, kClockManagerPolicyAgreement);

//CLOCK_SYS_SetConfiguration(&clockMan1_InitConfig0);

i = CLOCK_SYS_GetCoreClockFreq();

I2C0_SetClockConfiguration();

ADC_SetClockConfiguration();

}

EnableInterrupts;

}

all work fine but after the exit from this function LPSCI_HAL_SendDataPolling is called and the TDRE flag is set to 0 and the code stop in the while loop:

void LPSCI_HAL_SendDataPolling(UART0_Type * base,

const uint8_t *txBuff,

uint32_t txSize)

{

while (txSize--)

{

while (!UART0_BRD_S1_TDRE(base))

{}

LPSCI_HAL_Putchar(base, *txBuff++);

}

}

the problem is that i can't see the function that has tried to send data because i have this condition:

it is possible increase the number of function so i can reconstruct the function that call this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Daniele,

- After run here

how about continue to run ?

- " it is possible increase the number of function so i can reconstruct the function that call this? "

Do you meaning you want change the function of "LPSCI_HAL_SendDataPolling", yes , you can .

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

i have tried some solution in this days but nothing works.

I have define a static callback in the fsl_clock_manager

that do this (i have follow this

https://app-community.freescale.com/docs/DOC-329554):

clock_manager_error_code_t clockMan_uart0_callback(clock_notify_struct_t

notify, void * callbackData)

{

clock_manager_error_code_t result = kClockManagerSuccess;

switch (notify->notifyType) {

case kClockManagerNotifyBefore:

DbgConsole_DeInit();

break;

case kClockManagerNotifyRecover:

break;

case kClockManagerNotifyAfter:

CLOCK_SYS_SetLpsciSrc(0, kClockLpsciSrcOsc0erClk);

DbgConsole_Init(0, 115200, kDebugConsoleLPSCI);

break;

default:

result = kClockManagerError;

break;

}

/* Write user code here */

return result;

}

the clock surce of the uart0 is always the oscerclk

but the firmware continue to lock at the function

with the register setting as is

PS: i'm using FREERTOS

Il 23/02/2016 04:12, Alice_Yang ha scritto:

>

NXP Community

<https://community.freescale.com/?et=watches.email.thread>

>

fsl_debug problem change frequency

risposta da Alice_Yang

<https://community.freescale.com/people/Alice_Yang?et=watches.email.thread>

su /Kinetis Design Studio/ - Visualizza la discussione completa

<https://community.freescale.com/message/617635?et=watches.email.thread#617635>

>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Daniele,

From your screenshot, i see the TDRE bit has set to 1, so i think it can jump to the loop

while (!UART0_BRD_S1_TDRE(base))

Could you please test the demo code under KSDK1.3 on your board :

KSDK_1.3.0\examples\frdmkl46z\driver_examples\lpsci\lpsci_polling\kds

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, solved the problem with the timer using the function

CLOCK_SYS_SetPllfllSel(kClockPllFllSelPll); but with the fsl_debug the

problem stay on.

Il 02/03/2016 10:30, Alice_Yang ha scritto:

>

NXP Community

<https://community.freescale.com/?et=watches.email.thread>

>

fsl_debug problem change frequency

risposta da Alice_Yang

<https://community.freescale.com/people/Alice_Yang?et=watches.email.thread>

su /Kinetis Design Studio/ - Visualizza la discussione completa

<https://community.freescale.com/message/620493?et=watches.email.thread#620493>

>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Daniele,

After you change the clock of cpu, you need refer to the initialize code to configure the clock of UART,

and i have not see you re-configure the UART clock , and i don't know the "fsl_debug problem" detail,

so you can send your project to me , i can debug it , then check the problem .

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

any news?

--

*OPTOI GROUP *

Technical Dept.

Daniele Cortellazzi

***************************************************

OPTOELETTRONICA ITALIA S.r.l.

Via Vienna, 8

I-38121 Gardolo (TN) ITALY

Phone 0039 0461 991121

Fax 0039 0461 990164

daniele.cortellazzi@optoi.com

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

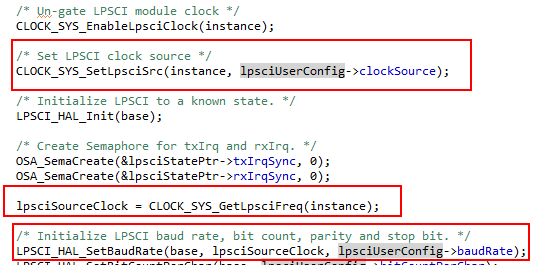

Hello Danniele,

I had intended to change the project correct then send o you , but

the project on my side sometimes can not run into the "main_task()",

for i know little about the RTOS, so i can only check the code without debug.

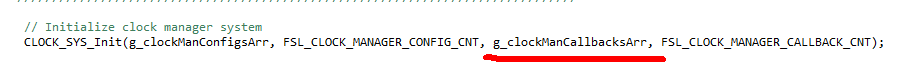

First , in the function of

the callback function will initialize the peripherals clock, for example the UART, and this needs to be

implemented manually , while in your project , it is null , so it have not update the uart clock .

And about the change clock configuration, i highly recommend you one demo , it use KSDK1.2 , while

the method is the same , you can refer to : https://community.freescale.com/thread/357115#524685

Hope it helps

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

i have just tried with the use of the callback function but same

problem. I have change some part in the code:

- remove the WAIT component in pex because i not use it

- i use the callback function for deinit e init the UART

(clockMan_uart0_callback)

to do the same things in the sample, the device still to not work.

In my project i use a 16mhz crystal but the frdm mount a 8mhz,

could be this to give you problem?

The firmware is very simple, it print "HELLO" and when the pin PTD6 is

pulled down the interrupt PORTC_PORTD_IRQHandler is called, the

CPU_Clock_Setting() function is executed and a change in frequency is

required.

Thanks

*

Il 16/03/2016 05:25, Alice_Yang ha scritto:

>

NXP Community

<https://community.freescale.com/?et=watches.email.thread>

>

fsl_debug problem change frequency

risposta da Alice_Yang

<https://community.freescale.com/people/Alice_Yang?et=watches.email.thread>

su /Kinetis Design Studio/ - Visualizza la discussione completa

<https://community.freescale.com/message/625200?et=watches.email.thread#comment-625200>

>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

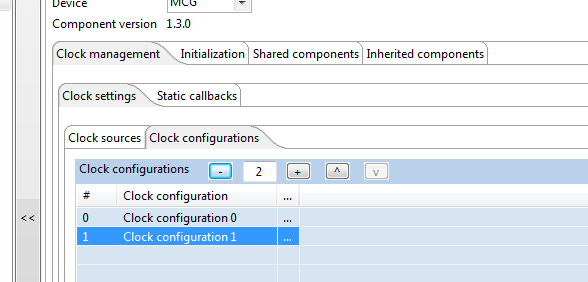

Hello Daniele,

For the component of "fsl_debug_console" use the UART, so , in order to

analysis easily , i create one new project on ksdk1.3 about the frdm-kl46(kl46z256),

add the fsl_lpsci component , also configure it to UART0 , pay attention , i configure

the PTA1 PTA2 as the UART0 pins.Set two clock mode , FEI and PEE,

use the "clock configuration1"(PEE) mode as the

initialize mode , then change it to FEI.

In the main function , first send "abc", after change the clock mode , send "def", also can check the

current core clock : syt_test = CLOCK_SYS_GetCoreClockFreq();

Please test it on your side , maybe you need change the Pins of UART .

Hope it helps

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

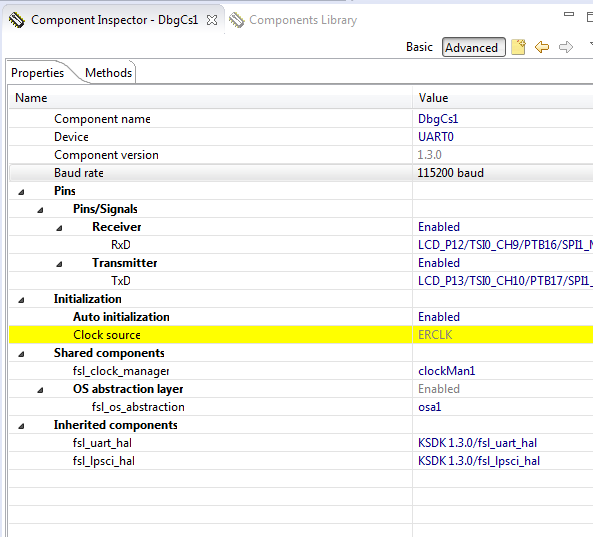

Hello Alice,

sorry for the delay in the response but i had work on other project. Yes

you sample is working fine, i have change the clock crystal to 16Mhz and

use the fsl_debug instead the uart library. The problem born when you

select the clock source of the fsl_debug. If i select the autoselect

all work , but if i select

it crush. There is a bag ....

I use the ERCLK because i have a system that can go in low power

reducing the frequency, using the external clock (16Mhz) directly for

clock the system i can turn off the PLL and FLL.

Attached the sample with external cystal set to 16Mhz and the fsl_debug,

if you try the two setting in one case work, in the other not.

Thanks

--

*OPTOI GROUP *

Technical Dept.

Daniele Cortellazzi

***************************************************

OPTOELETTRONICA ITALIA S.r.l.

Via Vienna, 8

I-38121 Gardolo (TN) ITALY

Phone 0039 0461 991121

Fax 0039 0461 990164

daniele.cortellazzi@optoi.com

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

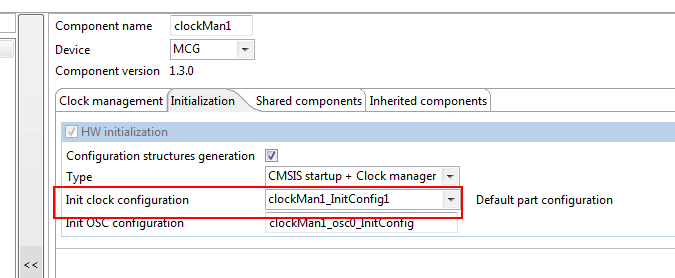

Hello Daniele,

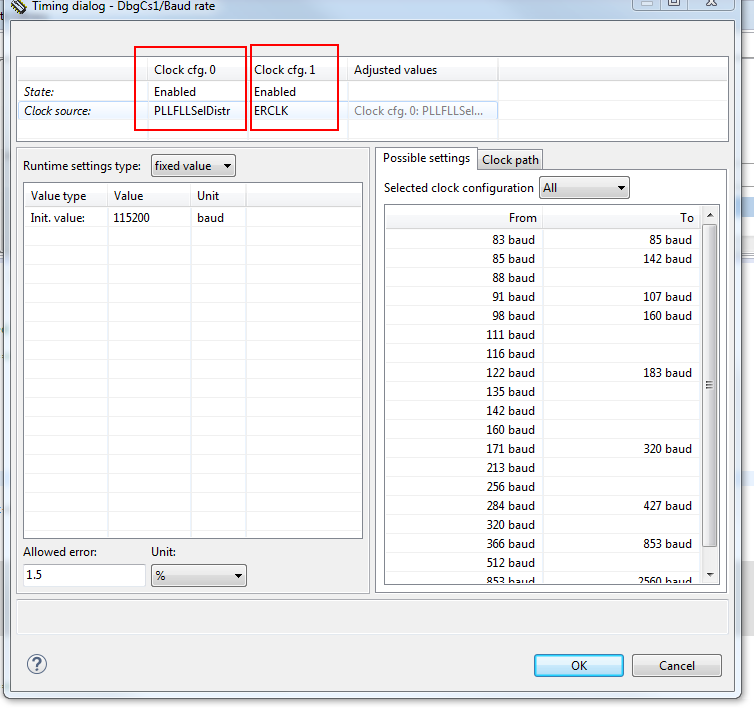

The Clock cfg0 is FEI, so we can not use the ERCLK as the clock source

of UART0. In the CFG1 PEE mode , we can use it , so you can configure the

fsl_debug_console component as this :

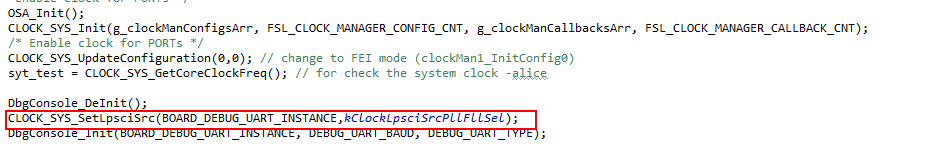

And in the code , please add

Pay attention that , my project is from PEE mode to FEI mode , so when it change to FEI mode,

configure the UART clock source as "kClockLpsciSrcPllFllSel ".

Hope it helps

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

attached there is the firmware. I'm using a kl46 with 16mhz crystal and

freertos. The function used are in:

- rtos_main_task.cwhere the init.c function is called and a

infinite loop print an "Hello"

- event.c where an interrupt PORTC_PORTD_IRQHandler call the

CPU_Clock_Setting function that change the frequency

Thanks

*

Il 07/03/2016 12:17, Alice_Yang ha scritto:

>

NXP Community

<https://community.freescale.com/?et=watches.email.thread>

>

fsl_debug problem change frequency

risposta da Alice_Yang

<https://community.freescale.com/people/Alice_Yang?et=watches.email.thread>

su /Kinetis Design Studio/ - Visualizza la discussione completa

<https://community.freescale.com/message/622056?et=watches.email.thread#comment-622056>

>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

yes with this sample it work. I have tried to disable the debug but same

proble happen with the TPM2 used like pwm. When i press a button the

function TPM_DRV_PwmStop(LCD_PWM_IDX, &LCD_PWM_ChnConfig0, 0); is called

and after that i switch the frequency:

if (CLOCK_SYS_GetCurrentConfiguration() != 1) {

error = CLOCK_SYS_UpdateConfiguration(1,

kClockManagerPolicyForcible);

//CLOCK_SYS_SetConfiguration(&clockMan1_InitConfig0);

i = CLOCK_SYS_GetCoreClockFreq();

//LPSCI_HAL_SetBaudRate(UART0_BASE_PTR, i, 115200);

I2C0_SetClockConfiguration();

ADC_SetClockConfiguration();

}

when the button is newely pressed i do

if(CLOCK_SYS_GetCurrentConfiguration() != 0){

error = CLOCK_SYS_UpdateConfiguration(0,

kClockManagerPolicyForcible);

//CLOCK_SYS_SetConfiguration(&clockMan1_InitConfig0);

i = CLOCK_SYS_GetCoreClockFreq();

//LPSCI_HAL_SetBaudRate(UART0_BASE_PTR, i, 115200);

TPM_DRV_SetClock(LCD_PWM_IDX, kTpmClockSourceModuleClk,

kTpmDividedBy32);

I2C0_SetClockConfiguration();

ADC_SetClockConfiguration();

}

to restore the cpu to higher frequency but when i call the function

TPM_DRV_PwmStart(LCD_PWM_IDX, &LCD_PWM_ChnConfig0, 0); it don't run

correctly. The MOD register is set to FFFFF bacause the function

CLOCK_SYS_GetPllFllClockFreq(); (called as in the image) return 0

Il 02/03/2016 10:30, Alice_Yang ha scritto:

>

NXP Community

<https://community.freescale.com/?et=watches.email.thread>

>

fsl_debug problem change frequency

risposta da Alice_Yang

<https://community.freescale.com/people/Alice_Yang?et=watches.email.thread>

su /Kinetis Design Studio/ - Visualizza la discussione completa

<https://community.freescale.com/message/620493?et=watches.email.thread#620493>

>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

the software remain in the infinite loop and can't exit, so my firmware is locked there. As visible in the image i see that the SendDataPolling is called by the debug_putc() but i can't reconstruct all the way. I can't see where the debug_putc is called so to debug the code, for do this i have to increase the number of nested function visible in kds.

Thanks