- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- MCUXpressoソフトウェアとツール

- :

- Kinetisデザインスタジオ

- :

- Debugger terminates session in middle of initialization

Debugger terminates session in middle of initialization

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, My name is Juan and I'm having trouble with KDS and Processor Expert, in particular component BitIO_LDD.

I'm using FRDM_KL05Z for one project, i need to read some GPIO Pins, so I've decided to use the component of PE mentioned above.

But, when I (or processor expert) initialize the component, it terminates automatically the debug session. I've debugged step by step and every time crashes in the middle of Init. Sometimes it even crash KDS IDE.

The function is: GPIO_DIR0_Init(DIR0);

And is defined:

LDD_TDeviceData* GPIO_DIR0_Init(LDD_TUserData *UserDataPtr)

{

/* Allocate device structure */

GPIO_DIR0_TDeviceDataPtr DeviceDataPrv;/* {Default RTOS Adapter} Driver memory allocation: Dynamic allocation is simulated by a pointer to the static object */

DeviceDataPrv = &DeviceDataPrv__DEFAULT_RTOS_ALLOC;

DeviceDataPrv->UserDataPtr = UserDataPtr; /* Store the RTOS device structure */

/* Configure pin as input */

/* GPIOA_PDDR: PDD&=~1 */

GPIOA_PDDR &= (uint32_t)~(uint32_t)(GPIO_PDDR_PDD(0x01));

/* Initialization of Port Control register */

/* PORTA_PCR0: ISF=0,MUX=1 */// Terminates debug session when running next line

PORTA_PCR0 = (uint32_t)((PORTA_PCR0 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x06)

)) | (uint32_t)(

PORT_PCR_MUX(0x01)

));

/* Registration of the device structure */

PE_LDD_RegisterDeviceStructure(PE_LDD_COMPONENT_GPIO_DIR0_ID,DeviceDataPrv);

return ((LDD_TDeviceData *)DeviceDataPrv);

}

Anyone have an idea on what can I do?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Juan,

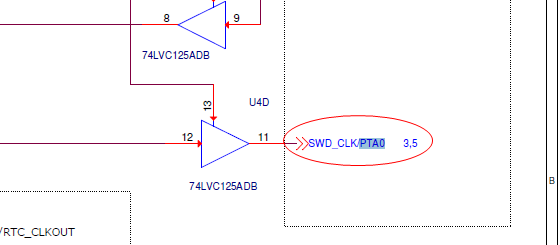

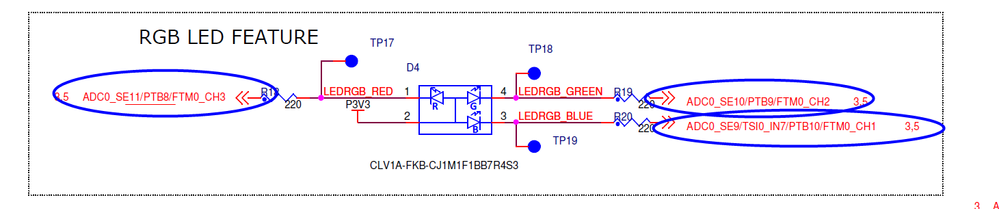

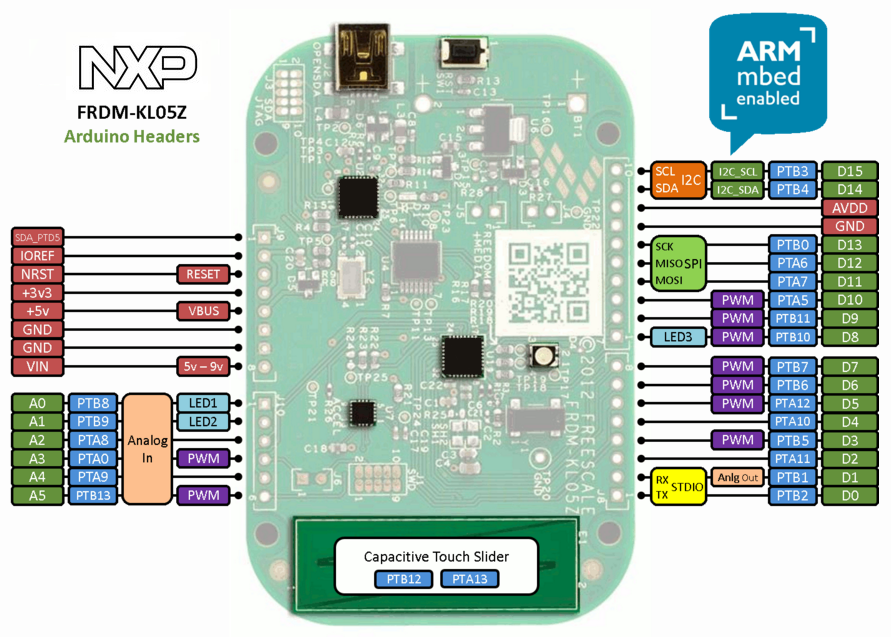

I have checked your code. Please have a look at the SCH for FRDM-KL05 board,

the PTA0 connect to SWD_CLK pin , it also means, we used it when debugging .

Please change another gpio that haven't used, for example , you can test the LDEs :

Hope it helps

Have a great day,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

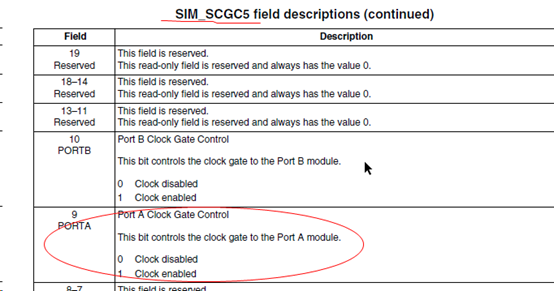

Hello Juan Diego Scarini ,

Have you enable the PORTA clock ?

And why you use the initialize funciont GPIO_DIR0_Init() , not the Bit1_Init() when

you use the component of BitIO_LDD .

If still can't work , please send your whole project to me, I will help you check it on my side .

Hope it helps

Have a great day,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

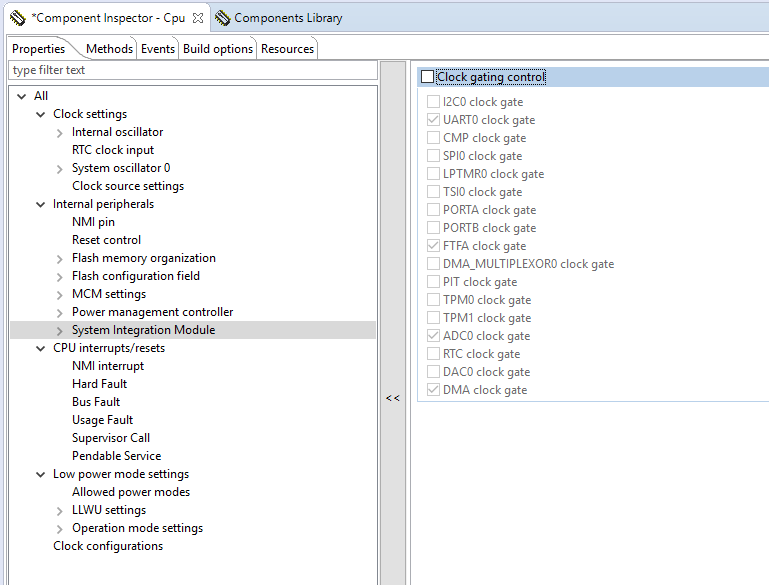

Hi Alice! Thank you for your answer.

Looking at what you said, i've checked PE Processor Component, SIM Module.

There I found that there was no clock gating on PORTA and PORTB (Ports that I use)

So I've enabled the Clock Gating Control and when I enable it, the PORTA and PORTB options enable automatically.

Well, I've deceided to run the code in debugging mode, but when it comes to the initialization part, It freezes! The fail is in the exact same point.

The SIM_SCGC5 has the correct value 0x780, but it still freezes on the same part:

PORTA_PCR0 = (uint32_t)((PORTA_PCR0 & (uint32_t)~(uint32_t)(PORT_PCR_ISF_MASK |PORT_PCR_MUX(0x06))) | (uint32_t)(PORT_PCR_MUX(0x01)));

And i've got no ideas on what to do...

Thank you

Juan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

HI Juan,

You can send attached your project througth Actions -> Edit ...,

or you can create a case to NXP support as I told you .

BR

Alice

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Juan,

I have checked your code. Please have a look at the SCH for FRDM-KL05 board,

the PTA0 connect to SWD_CLK pin , it also means, we used it when debugging .

Please change another gpio that haven't used, for example , you can test the LDEs :

Hope it helps

Have a great day,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you!

I've used this image as a guide for connection:

But, nevermind, i've marked that pin as SWD in my printed copy, thanks again!

Juan