- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 製品フォーラム

- :

- デジタルシグナルコントローラ

- :

- Re: MC56F84789 Problem with DMA SCI - receiver idle interrupt

MC56F84789 Problem with DMA SCI - receiver idle interrupt

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

MC56F84789 Problem with DMA SCI - receiver idle interrupt

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I have problem with DMA SCI on receiver idle interrupt.

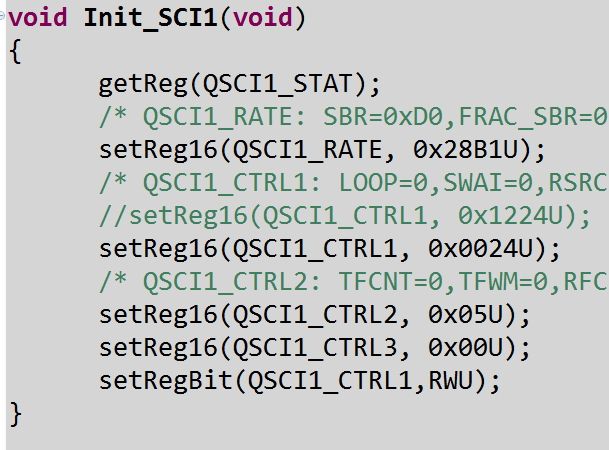

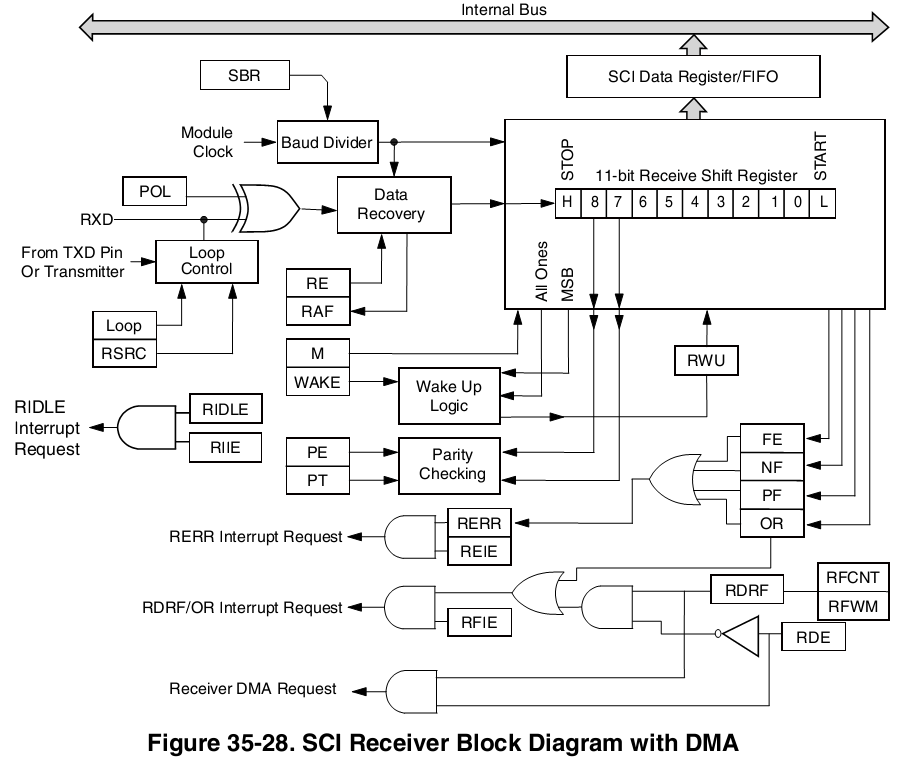

I wrote the codes of SCI receiver by DMA and it works well.

But when I try to add receiver idle interrupt, I can not find where the receiver idle interrupt vecteor is.

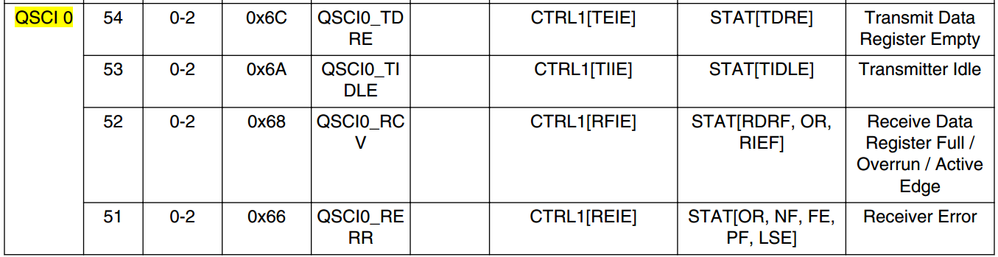

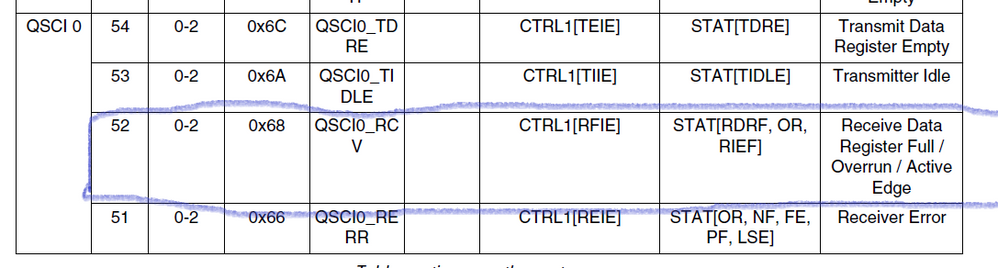

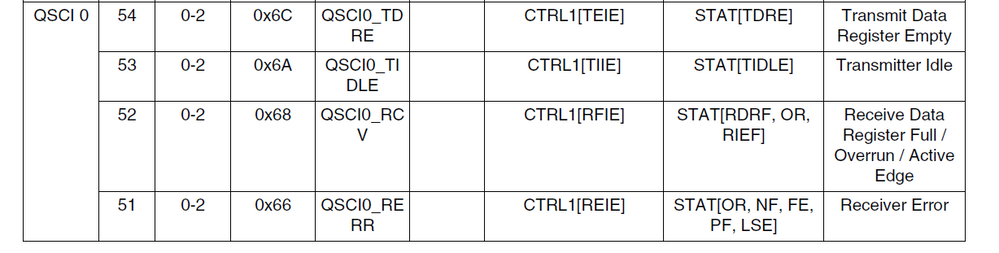

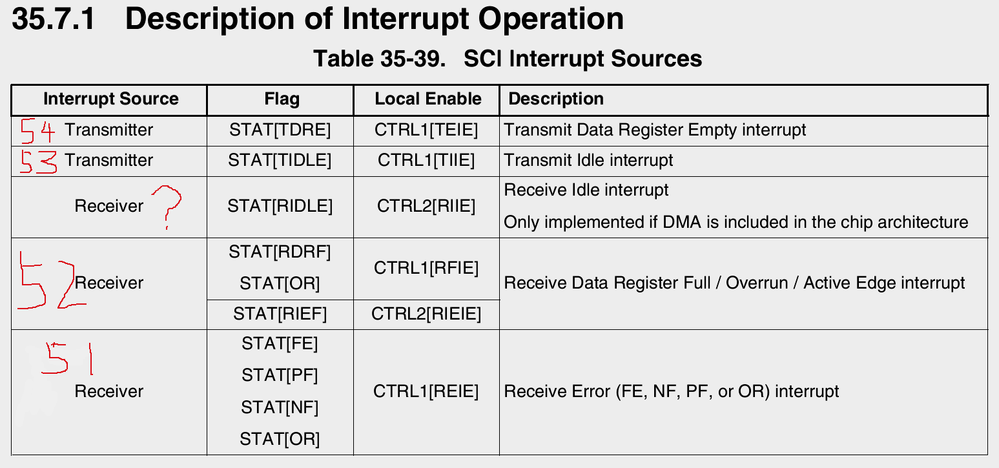

I have to search the whole <MC56F847xx Reference Manual> but no more information except bellows:

But it does not exist in Table 3-10. Interrupt Vector Table:

And I can not find any relative information in CodeWarrior PE.

Please help me, thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, WangJun,

I suppose that the Receiver idle can trigger interrupt vector 52. You can enable the Receiver idle interrupt by setting the RIIE bit QSCIx_CTRL2, in the ISR of vector 52, you can check the RIDLE bit in QSCIx_STAT, if it is set you can see that Receiver idle happens.

As a test, in the ISR of vector 52, you can check the RIDLE bit, if it is set, toggle a GPIO. You can check the GPIO pin waveform to know if the receiver idle happens or not.

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Mr.rong,

Thank you for your answer.

RIDLE bit is set after a message received, but it does not trigger vectors from 51 to 54.

It seems an individual vector, but where?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Jun,

Pls refer to the vector table, there are 2 interrupt vectors for the SCI0 receiver, so I suspect the idle interrupt of receiver is included in vector 51 or 52, especially 52.

You can have a try by generating the receiver interrupt and set a break point in two ISR and check which is entered.

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Mr. rong,

I have checked 51 and 52 many times, no one can be entered after Ridle flg set.

From Table 35-39 I attached days ago, I think there is an independent vector for Ridle.

thanks a lot

Jun Wang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,WangJun,

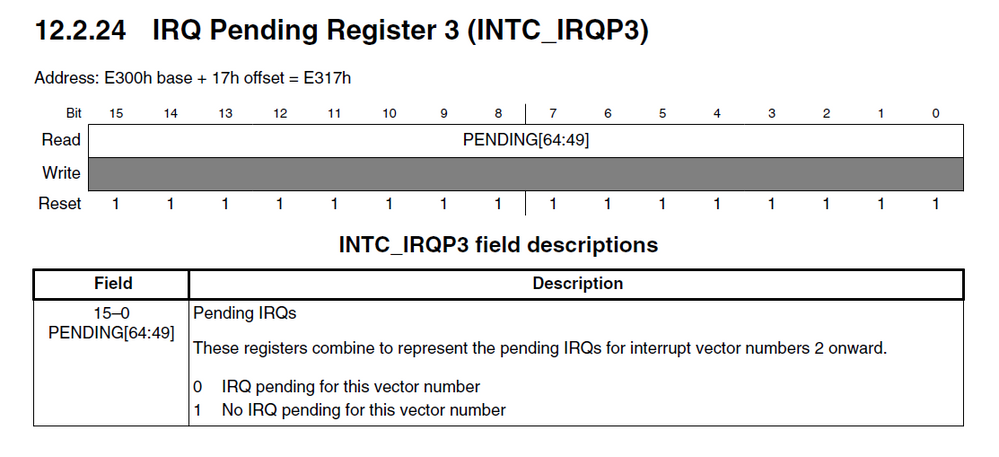

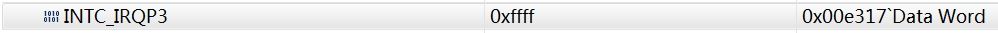

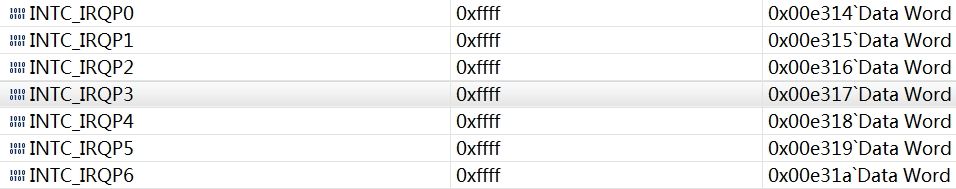

How about checking the INTC_IRQP3 reg to know if the SCI receiver idle interrupt happens or not?

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Mr.rong

any new information?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, WangJun,

I got feedback from design team, the SCI0 Receiver idle interrupt is not routed to interrupt table vector by mistake, so SCI0 receiver idle interrupt can not be triggered. We will document the issue in the errata.

Thank you for pointing the error.

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Mr.rong

I tested many times accordding to your suggestion.

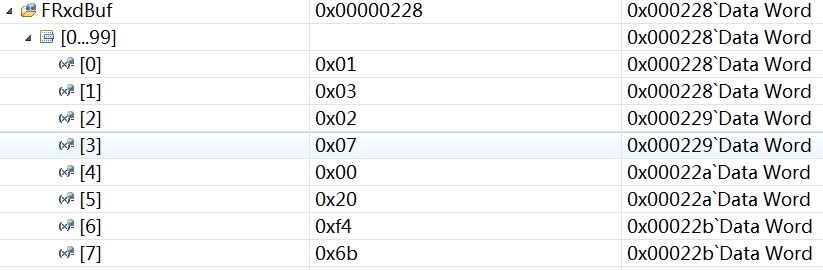

I enabled the RFIE & RIIE, and the DMA transported whole message correctly as below:

when a message ended, I checked the relative registors as bellow: RIDLE Flag is set.

but no any interrupt requist pending up:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

No any interrupt request.