- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- ColdFire/68K Microcontrollers and Processors

- :

- QSPI Clock

QSPI Clock

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have a problem with SPI transfer between MCF52259 and ADS1278 data converter. The clock from 52259 is generating but there are delays between them and thus ADS1278 is not working properly.

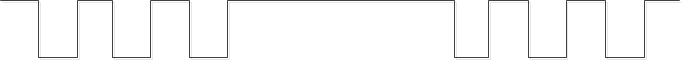

Here is how the clock signal looks like.

The output from ADS1278 is 24-bit which it is sending out on SPI protocol.

I configured the 52259 QSPI registers as follows. I am not sending out anything QSPI_DOUT pin as I configured it as GPIO which is always low. Also, I am not using any QSPI_CS0, QSPI_CS1, QSPI_CS2 and QSPI_CS3 pins so I masked it out.

MCF_QSPI_QMR = MCF_QSPI_QMR_MSTR |

MCF_QSPI_QMR_BITS(12) |

MCF_QSPI_QMR_CPOL |

MCF_QSPI_QMR_CPHA |

MCF_QSPI_QMR_BAUD(2);

MCF_QSPI_QWR = MCF_QSPI_QWR_WREN |

MCF_QSPI_QWR_WRTO |

MCF_QSPI_QWR_ENDQP(15) |

MCF_QSPI_QWR_NEWQP(0);

MCF_QSPI_QIR = MCF_QSPI_QIR_ABRTE |

MCF_QSPI_QIR_SPIFE;

for( request = 0; request <= 15; request++ )

{

MCF_QSPI_QAR = (WORD)(MCF_QSPI_QAR_CMD + request);

MCF_QSPI_QDR = MCF_QSPI_QDR_BITSE |

MCF_QSPI_QDR_QSPI_CS3 |

MCF_QSPI_QDR_QSPI_CS2 |

MCF_QSPI_QDR_QSPI_CS1 |

MCF_QSPI_QDR_QSPI_CS0;

}

MCF_QSPI_QWR &= ~(MCF_QSPI_QWR_HALT);

MCF_QSPI_QDLYR = MCF_QSPI_QDLYR_SPE;

Any help will be highly appreciated.

Regards.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are not setting MCF_QSPI_QDR_QSPI_DT in MCF_QSPI_QDR so the "Standard delay after transfer" of (17 / fSys) is being applied. You should set MCF_QSPI_QDR_QSPI_DT and then set QDLYR[DTL] to zero. That might get you "no gaps"

The QSPI doesn't seem to be able to be set in a mode where it generates continuous clocks. It only generates clocks when it reads and writes data. You can't use it to generate the CLK input to the ADS1278. You can only use it to generate the SCLK input. Have you tied these together?

If you haven't tied the clocks I don't see why you're worrying about this The ADS1278 doesn't care if there are gaps in the SCLK stream, as long as its CLK stream is continuous.

It is a painful and non-standard SPI interface anyway. You have to wait (in software or with interrupts I'm guessing) for the DRDY pin to drop, and only then can you start the SPI generating clocks to read the data stream. It would be far more "standard" if it took a chip-select.

Since you're trying to read 24-bit conversion results, it might be more convenient for data packing if you programmed the QSPI to read groups of three bytes rather than two groups of 12 bits per conversion. You can read 8 at a time in the one command as you're doing with 12 bits, or you could read 5 results at a time with 8 bits (four would be easier to code). I think you're better off the way you're doing it with 12 bits though.

Tom

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you please supply an actual capture of the clock signal rather than a partial sample? Preferably covering more than one transfer.

Tom

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is the QSPI clock signal captured from the scope. The QSPI baud rate is set to 2 so the clock is 20 MHz but there are delays in clock signal. I need to get rid of these delays.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are not setting MCF_QSPI_QDR_QSPI_DT in MCF_QSPI_QDR so the "Standard delay after transfer" of (17 / fSys) is being applied. You should set MCF_QSPI_QDR_QSPI_DT and then set QDLYR[DTL] to zero. That might get you "no gaps"

The QSPI doesn't seem to be able to be set in a mode where it generates continuous clocks. It only generates clocks when it reads and writes data. You can't use it to generate the CLK input to the ADS1278. You can only use it to generate the SCLK input. Have you tied these together?

If you haven't tied the clocks I don't see why you're worrying about this The ADS1278 doesn't care if there are gaps in the SCLK stream, as long as its CLK stream is continuous.

It is a painful and non-standard SPI interface anyway. You have to wait (in software or with interrupts I'm guessing) for the DRDY pin to drop, and only then can you start the SPI generating clocks to read the data stream. It would be far more "standard" if it took a chip-select.

Since you're trying to read 24-bit conversion results, it might be more convenient for data packing if you programmed the QSPI to read groups of three bytes rather than two groups of 12 bits per conversion. You can read 8 at a time in the one command as you're doing with 12 bits, or you could read 5 results at a time with 8 bits (four would be easier to code). I think you're better off the way you're doing it with 12 bits though.

Tom