- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- CodeWarrior

- :

- QorIQ用CodeWarrior

- :

- T2081 - CodeWarrior

T2081 - CodeWarrior

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

T2081 - CodeWarrior

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

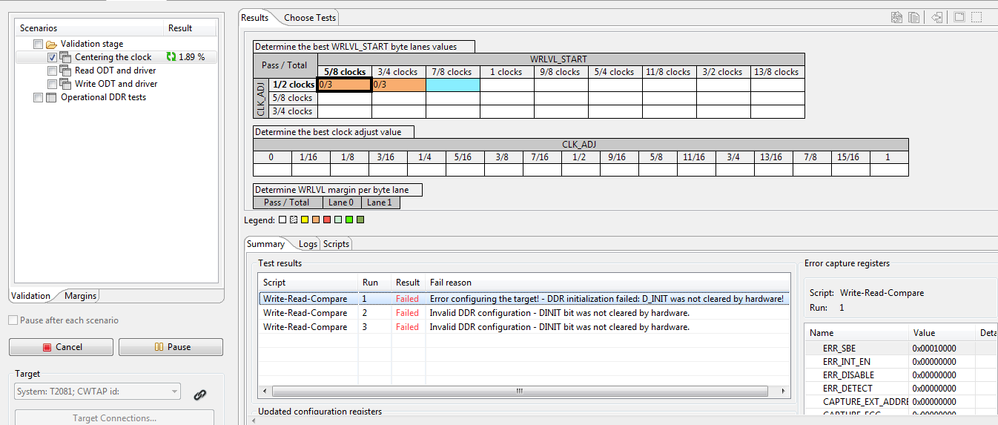

Hello community,

i have some trouble with CodeWarrior and T2081 CPU.

I am trying to valid the DDR with the DDR-configuration (CodeWarrior).

But when i start a DDR-test it failed everytime and the CCS say this:

CCSAPI connection #1 accepted from ELSTJ-W.tq-net.de at Thu Apr 12 11:40:21 2018

check_min_version(serverh=0,*version)

api version: 00000004 00000006

available_connections(serverh=0,*count,*cc)

connections: {0,73,0xa9fee4a5}

cc_version(serverh=0,cc_index=0,index=0,*version)

config_chain(serverh=0,cc=0,count=1,*devlist,*generic)

devlist: t4amp

reset_to_debug(serverh=0,cc=0)

ERROR(39): Subcore error encountered during multicore operation

parse_error_ext(coreh.{serverh=0,cc_index=0,chain_pos=0}, 39)

error: T2080: HRESET occurred during transaction

CCSAPI connection #1 from ELSTJ-W.tq-net.de closed at Thu Apr 12 11:40:22 2018

Can anyone help me please.

Thanks in advance.

Best regards,

Juergen

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello again,

i think i have the issue fixed. It was some HW issue with HRESET.

But after this i have the next failure with DDR initialization.

"Error configuuring the target! - DDR initialization failed: D_INIT was not cleared by hardware!

Can anyone help me with this.

Thanks in advance.

Best regards,

Juergen

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Juergen,

Please check whether the RCW configuration is valid for DDR clock configuration.

Please refer to AN3940 - Hardware and Layout Design Considerations for DDR3 SDRAM to check DDR hardware design.

If there is DDR SPD on your custom board, please use reading from SPD to create a QCVS DDR project.

If there is no SPD on your target board, please create a QCVS DDR project with the default configuration and configure the DDR related properties in the DDR QCVS project according to the DDR datasheet, then generate the initial DDR controller configuration and connect to the target board to do optimization and validation.

For details, please refer to DDRv user manual https://www.nxp.com/docs/en/user-guide/QCVS_DDR_User_Guide.pdf?fsrch=1&sr=10&pageNum=1.

If your problem remains, please also attach the CCS console log.

Thanks,

Yiping

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Yiping,

thanks for your help.

In the meantime I have found the problem-source.

It was a reset-timing that occured with the Codewarrior.

Best regards,

Juergen