- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- CodeWarrior

- :

- MCU用CodeWarrior

- :

- Re: OpenSDA debugging problem when relocating code to RAM on KEAZ128

OpenSDA debugging problem when relocating code to RAM on KEAZ128

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dears,

We are working on a design based on Kinetis KEAZ128. To boost the performance of poor 40MHz Cortex M0+ core, we decided to put some key C functions into RAM to avoid Flash ROM access latency.

We have studied the document below and modified our code as chaptor 4.3:

Relocating Code and Data Using the CW GCC Linke... | NXP Community

https://community.nxp.com/docs/DOC-101433

With Codewarrior 10.7, code built with no error, .map file looks also OK, but problem happened when we begin to debug the code on a FRDM-KEAZ128 board with OpenSDA, here are error messages:

INF: CMD>VC

INF: Verifying object file CRC-16 to device ranges ...

INF: block 00000000-000000BF ...

INF: Ok.

INF: block 00000400-0000B8FF ...

INF: Ok.

INF: block 0000B880-0000B897 ...

INF: CRC-16 Error in block. (File = $9AC8, Device = $0000)

ERR: Error verifying flash of device

ERR: Error occured during Flash programming.

INF: Warning 17927. Target MCU mismatch. Download performance limited. See http://www.pemicro.com/opensda/pe_tools.cfm for information on debugging external processors.

GDI: => DI_ERR_FATAL

GDI: Memory access performed successfully

We guess this should be caused by the re-locating, but have no idea how to deal with.

Anyone can help?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Wang,

I haven't the FRDM-KEAZ128 board, I test your project on TRK-KEA128 board,

when use the P&E debug mode , the same error with yours.

While when I change the Opensda to J-link interface, it can work well.

So could you please update your board to J-link , refer to Quick Start of your board.

BR

Alice

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I reproduced the issue and it's indeed a defect.

I'd recommend you to use Flash Programmer instead and then connect to the device or use J-link Firmware as suggested by Alice as a workaround:

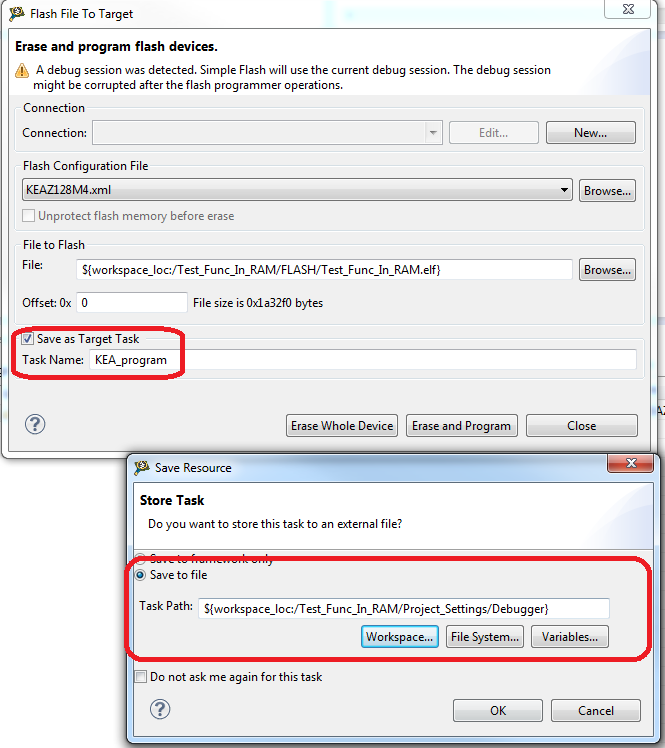

1) create a target task that programs the elf file to the device and save it to the project directory:

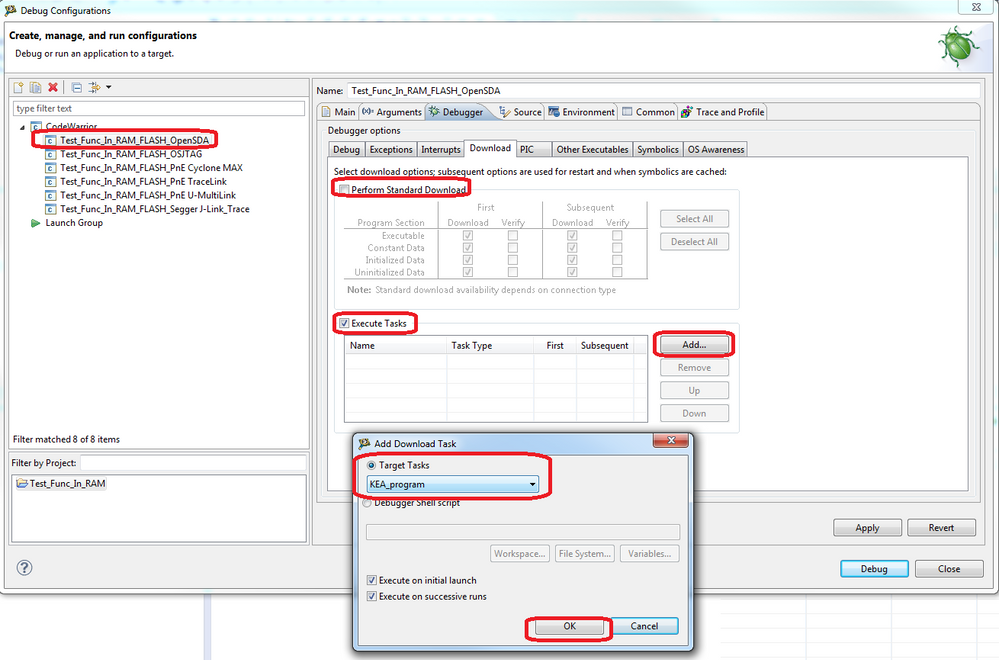

2) adjust the debug configuration so it does not use the default download but executes the target task instead:

3) apply and now if you press "Debug" you should always be able to program the mcu.

Hope it helps.

Stan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Stan,

We've tried your proposal and it works well. Probably we prefer OpenSDA because we have no license available for J-Link Flasher.

Thanks a lot.

Walter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Wang,

Please share your project , it will be better to point the code about relocating code into RAM.

BR

Alice

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Alice,

I've created a very simple project to test the ram function but still failed, see attached. It was created by CW10.7.

Changes are made according to the article https://community.nxp.com/docs/DOC-101433

(Due to company policy I cannot send you our project, sorry for this.)

Also, I just paste codes here for easy discussion, it's very simple.

********* my code *******************************************

word Value;

void RAM_Func(word * val);

/*lint -save -e970 Disable MISRA rule (6.3) checking. */

int main(void)

/*lint -restore Enable MISRA rule (6.3) checking. */

{

/* Write your local variable definition here */

/*** Processor Expert internal initialization. DON'T REMOVE THIS CODE!!! ***/

PE_low_level_init();

/*** End of Processor Expert internal initialization. ***/

/* Write your code here */

/* For example: for(;;) { } */

Value=0;

for(;;){

RAM_Func(&Value);

}

/*** Don't write any code pass this line, or it will be deleted during code generation. ***/

/*** RTOS startup code. Macro PEX_RTOS_START is defined by the RTOS component. DON'T MODIFY THIS CODE!!! ***/

#ifdef PEX_RTOS_START

PEX_RTOS_START(); /* Startup of the selected RTOS. Macro is defined by the RTOS component. */

#endif

/*** End of RTOS startup code. ***/

/*** Processor Expert end of main routine. DON'T MODIFY THIS CODE!!! ***/

for(;;){}

/*** Processor Expert end of main routine. DON'T WRITE CODE BELOW!!! ***/

} /*** End of main routine. DO NOT MODIFY THIS TEXT!!! ***/

/* END main */

__attribute__ ((section(".ramfunc"))) void RAM_Func(word * val) //The RAM function

{

(* val)++;

return;

}

********* Changes in linker setting file ProcessorExpert.ld *******************************************

/* Initialized data sections goes into RAM, load LMA copy after code */

.data : AT(___ROM_AT)

{

. = ALIGN(4);

_sdata = .; /* create a global symbol at data start */

*(.data) /* .data sections */

*(.data*) /* .data* sections */

*(.ramfunc) /* My newly defined RAM function area */

. = ALIGN(4);

_edata = .; /* define a global symbol at data end */

} > m_data

Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Wang,

I haven't the FRDM-KEAZ128 board, I test your project on TRK-KEA128 board,

when use the P&E debug mode , the same error with yours.

While when I change the Opensda to J-link interface, it can work well.

So could you please update your board to J-link , refer to Quick Start of your board.

BR

Alice

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Alice,

The RAM function is running properly after I updated my FRDM board FW to J-link FW (downloaded from Segger) and change debug profile to JLink.

Thank you for the feedback.