- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- CodeWarrior

- :

- CodeWarrior開発ツール

- :

- Codewarrior Tap connect MPC8280 Issue.

Codewarrior Tap connect MPC8280 Issue.

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Codewarrior Tap connect MPC8280 Issue.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am new to freescale mcus. Now I am working on a MPC8280 Board using Codewarrior Tap. I met a issue when I connect MPC8280 using codewarrior tap. I describe it as following.

I pull up nRSTCOF to use internal configuration word which is zero. And I Successfully connect Codewarrior Tap to 8280. I can access CPU register like MSR. But I can not get access to memory map register like BR1,OR1. I don't know why? any one can help?

Plus I am using CW 8.8

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

请问你解决这个问题了吗?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Dong Carlles,

Are you trying to view from the debugger register window, or view from memory window, or access from software code?

Regards

Lunmin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes, I am trying to access the configuration registers when I view the debugger register. But it fails. I can only access the G2_LE core registers like MSR. But I can not access the configuration register like BR0 BR1..etc.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Dong Carlles,

Sorry for late, can you please take a photo shot of the failure?

Regards

Lunmin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,lunminliang,

Thank you for response.

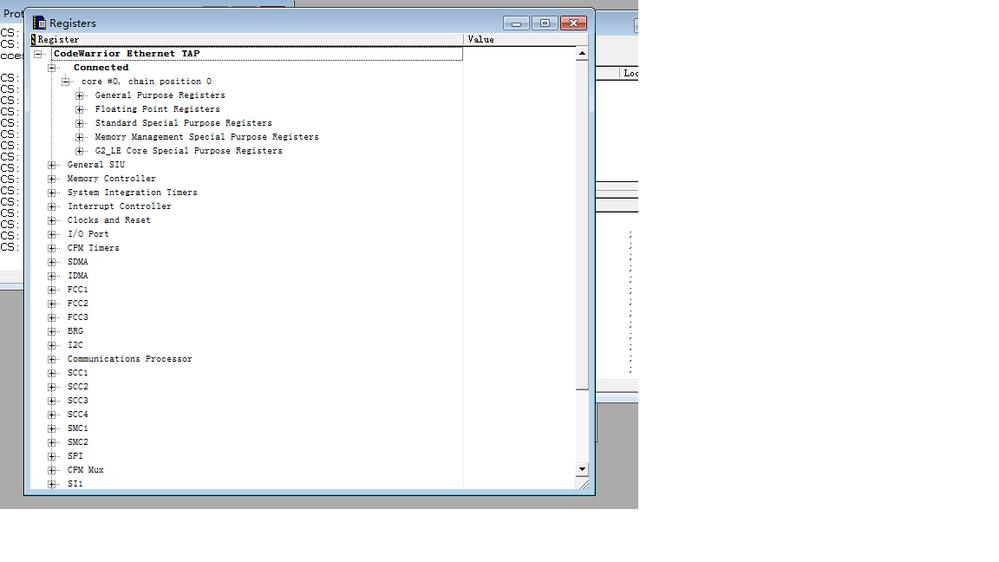

- Figure one show that I can connect to the MPC8280 as following.

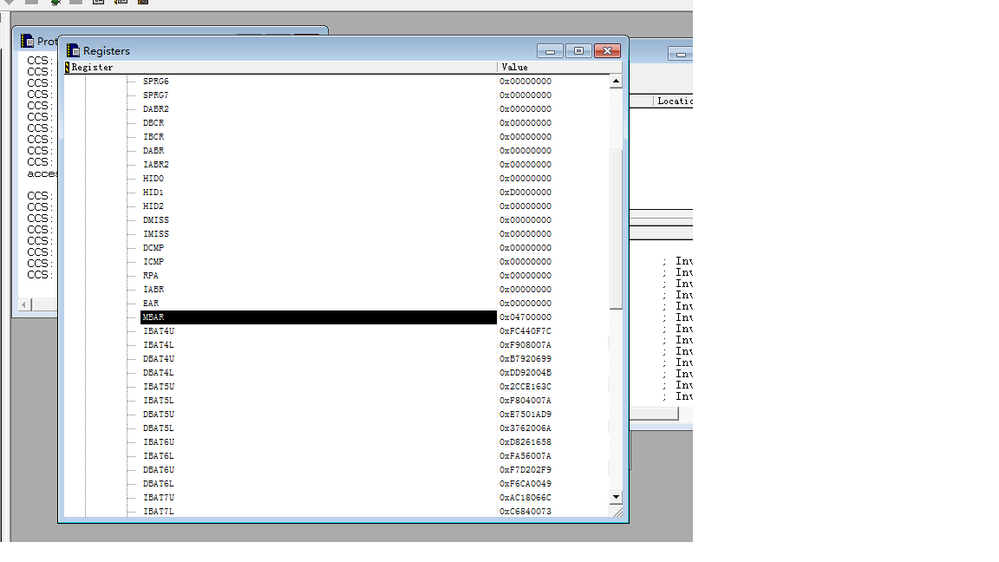

2, Figure w show that I can get access to the 8280 core.

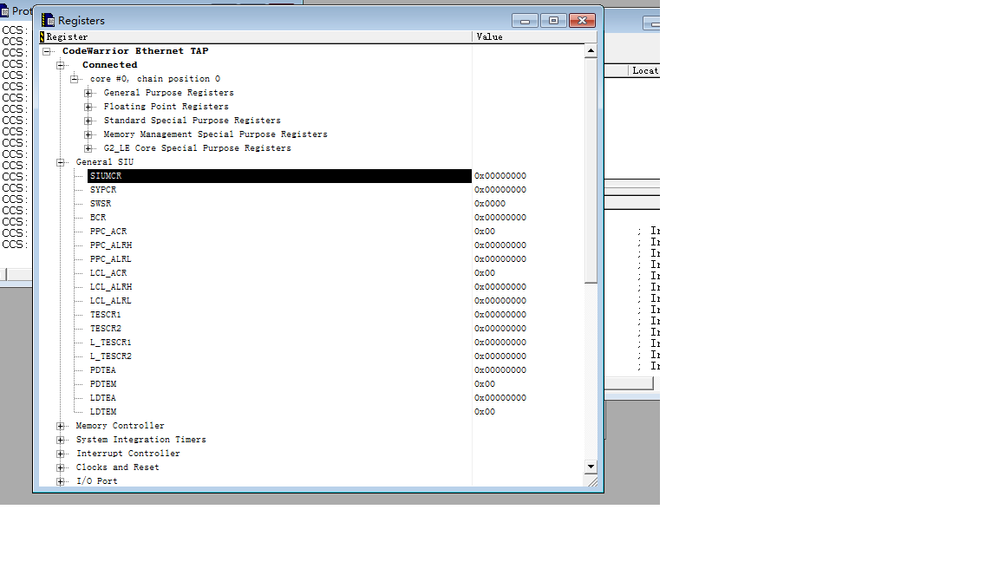

3. Figure three show that I can not access other registers. It is all zeros. And I cannot modify it.

Hope you can give some instruction on this. Thank you.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Dong Carlles,

Do you have a proper .cfg file for the connection?

Regards

Lunmin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I write a .cfg file but I seems have no affection to this. No matter how I modify it. It just perform the same.

Here is the configure file content.

writereg MBAR 0x0f000000

writemmr IMMR 0x01000000

writereg MBAR 0x01000000

#Main System Clock Configuration Registers

writemmr SYPCR 0xFFFFFF81 # SYPCR: turn off watchdog timer

writemmr SCCR 0x00000001 # Force baud rate clock divisor = 16

writemmr RMR 0x0001 # generate reset when core enters checkstop state.

# Setup the chip selects

# CS0 - 32MB flash

writemmr BR0 0xFE001001

writemmr OR0 0xFE000876

# CS1 - 8MByte(2*16bits + 2*16bits) SRAM

writemmr BR1 0x10001801

writemmr OR1 0xFF800876

writemmr MPTPR 0x2000 # MPTPR: Set the Memory Periodic Timer Prescaler

writemmr PSRT 0x1F # set 60x Bus assigned SDRAM Refresh Timer (PSRT) ~ 15.6us

writemmr SIUMCR 0x05340C00 # Set SIU configuration bits

writemmr TESCR1 0x00004000 # 60x bus data errors disabled

writemmr L_TESCR1 0x00004000

writereg MSR 0x3002 # Machine Mode Register

From my view, after I write MBAR, then I can write and read at least IMMR. And I try to just write MBAR and IMMR. I still can not access the IMMR. It still stay on zero.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Plus: MPC8280 will also reset after about 20~30 seconds.