- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- CodeWarrior

- :

- Classic/Legacy CodeWarrior

- :

- No linker command file input for section '.boot' in file

No linker command file input for section '.boot' in file

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

No linker command file input for section '.boot' in file

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using MPC5553, added some 3rd party stack and while compilation met with the below error/warnings,

Need help for the same.

I am guessing this is related to linker command but not sure about it.

I do have internal and external RAM along with the flash.... Do you suggest any memory allocation/alignment or something...?

appreciated any kind of hint...

refer below the error:

========================================================================================

No linker command file input for section '.boot' in file 'abc\MPC55xx_init.o'.

Output section '.boot' will be created.

Link Error : Small data sections must have their own output sections specified in the linker command file.

No linker command file output section '.sbss2'.

Link failed.

========================================================================================

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

this message tells you that some code was placed to a section (.boot) which does not exist in your linker file. So, it's necessary to create such section.

Here is simple example how to place a code/function to specific segment:

In linker file:

MEMORY

{

...

my_flash: org = 0x00004000, len = 0x00002000 //just example

...

}

SECTIONS

{

...

.boot (VLECODE) LOAD (ADDR(my_flash)):{

} > my_flash

...

}

In c file:

#pragma push

#pragma section code_type ".boot"

void test(void)

{

}

#pragma pop

Then you can check map file and s-record file that the function is really placed to that section.

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Lucas for you valuable input,

I am one step ahead and need further help, appreciated.

I have my code that runs external RAM support, below is my .lcf file snippet

here if you see, I had to add .sbss2 section because of the error

=====================================================================

MEMORY

{

/**** Size in Kilo Byte (x 1024bytes) ****/

interrupts_flash: org = 0x00020000, len = 0x00002000 // 8 KiB 0.0078125 MiB

resetvector: org = 0x00022000, len = 0x00000008 // 8(32) bytes 0.0000305176 MiB

Identity_flash: org = 0x00022008, len = 0x00000010 // 16 bytes

init: org = 0x00022020, len = 0x00000FE0 // 4064 bytes 0.0038757324 MiB

internal_flash: org = 0x00023000, len = 0x000DD000 // 880 KiB 0.86328125 MiB

CoDeSys_flash: org = 0x00100000, len = 0x00080000 // 512 KiB 0.5000 MiB

//-----------------------------

// 1536 KiB 1.5000 MiB

external_ram: org = 0x20000000, len = 0x00150000 // 1344 KiB 1.1875 MiB

stack : org = 0x20150000, len = 0x00020000 // 128 KiB 0.1250 MiB

heap : org = 0x20170000, len = 0x00090000 // 576 KiB 0.6875 MiB

//-----------------------------

// 2048 KiB 2.0000 MiB

internal_ram: org = 0x40000000, len = 0x0000F000 // 61 KiB 0.0614 MiB

SimVar_ram: org = 0x4000F000, len = 0x00000800 // 2 KiB 0.02 MiB

CodeSysVar_ram: org = 0x4000F800, len = 0x00000800 // 2 KiB 0.02 MiB

}

/* This will ensure the rchw and reset vector are not stripped by the linker */

//FORCEACTIVE { "bam_rchw" "bam_resetvector"}

//BIN_FILE_TYPE(MULTIPLE_BIN_FILES) // generates multiple .bin files

SECTIONS

{

/*.boot LOAD (0x00000000) : {} > boot_flash *//* LOAD (0x0) prevents relocation by ROM copy during startup */

GROUP :

{

.entry LOAD (0x00022020) :

{

*(.entry)

.=ALIGN(0x10);

}

.init LOAD (0x00022020 + SIZEOF(.entry) ) :

{

*(.init)

}

} > init

GROUP : {

/* Note: _e_ prefix enables load after END of that specified section */

.ivor_branch_table (TEXT) LOAD (ADDR(interrupts_flash)) : {}

.intc_hw_branch_table (TEXT) LOAD (_e_ivor_branch_table) ALIGN (0x800) : {}

.ivor_handlers (TEXT) LOAD (_e_intc_hw_branch_table) : {}

/* Each MPC555x handler require 16B alignmt */

} > interrupts_flash

GROUP : {

.intc_sw_isr_vector_table ALIGN (2048) : {} /* For INTC in SW Vector Mode */

.text : {

*(.text)

*(.rodata)

*(.ctors)

*(.dtors)

*(.init)

*(.fini)

*(.eini)

. = (.+15);

}

.sdata2 : {}

.sbss2 : {}

extab : {}

extabindex : {}

. = ALIGN(0x10);

__FASTCODE_ROM = .;

} > internal_flash

GROUP : {

__FASTCODE_RAM = .;

.funcInRam LOAD (__FASTCODE_ROM) : {

*(.funcInRam)

. = ALIGN(0x10);

}

. = ALIGN(0x10);

__FASTCODE_END = .;

__DATA_ROM_START = __FASTCODE_ROM + __FASTCODE_END - __FASTCODE_RAM;

.data (DATA) LOAD(__DATA_ROM_START) : {}

.sdata (DATA) LOAD(__DATA_ROM_START + SIZEOF(.data)) : {}

.sbss (BSS) : {}

.bss (BSS) : {}

.PPC.EMB.sdata0 : {}

.PPC.EMB.sbss0 : {}

} > external_ram

.identity LOAD (0x00022008): {} > Identity_flash

.variables LOAD(ROMADDR(.sdata)+SIZEOF(.sdata)) : {} > internal_ram

.__Simulink_ram LOAD(ROMADDR(.variables)+SIZEOF(.variables)) : {} > SimVar_ram

.__CodeSys_ram LOAD(ROMADDR(.__Simulink_ram)+SIZEOF(.__Simulink_ram)) : {} > CodeSysVar_ram

}

/* Freescale CodeWarrior compiler address designations */

_stack_addr = ADDR(stack)+SIZEOF(stack);

_stack_end = ADDR(.bss) + SIZEOF(.bss);

_heap_addr = ADDR(heap);

_heap_end = ADDR(heap)+SIZEOF(heap);

__IVPR_VALUE = ADDR(interrupts_flash);

/* L2 SRAM Location (used for L2 SRAM initialization) */

L2SRAM_LOCATION = 0x40000000;

AXM_0321_EXTERNAL_RAM = 0x20000000;

====================================================================

project compiles correctly, but it generates new warnings as below

+++++++++++++++++++++++++++++++++++++

multiply-defined: '__start' in Runtime.PPCEABI.E.UC.a in the file __start.o

Previously defined in __start.o

ignored: '__start' in Runtime.PPCEABI.E.UC.a from the file __start.o

multiply-defined: '__copy_rom_section' in Runtime.PPCEABI.E.UC.a in the file __start.o

Previously defined in __start.o

ignored: '__copy_rom_section' in Runtime.PPCEABI.E.UC.a from the file __start.o

multiply-defined: '__init_bss_section' in Runtime.PPCEABI.E.UC.a in the file __start.o

Previously defined in __start.o

ignored: '__init_bss_section' in Runtime.PPCEABI.E.UC.a from the file __start.o

Overlap of the ROM image address of extab section with executable address of .sbss2 section.

Overlap of the ROM image address of extab section with executable address of extab section.

Overlap of the ROM image address of extabindex section with executable address of extabindex section.

+++++++++++++++++++++++++++++++++++++

Interstingly, I see that in MAP file, there are overlap and I dont know why it is coming and how to get rid of this warnings. when these warnigns are available, my code is not working correclty.

*************************************************

Memory map:

Starting Size File ROM RAM Buffer S-Record Bin File Bin File

address Offset Address Address Line Offset Name

.entry 00022020 00000000 00000360 00022020 00022020 0 00000000 6026641-008_(size3_5_production_bootloadable).bin

.ivor_branch_table 00020000 00000000 00000360 00020000 00020000 0 00000000 6026641-008_(size3_5_production_bootloadable).bin

.intc_hw_branch_table 00020000 00001354 00000800 00020000 00020000 2 00000000 6026641-008_(size3_5_production_bootloadable).bin

.ivor_handlers 00021354 00000000 00001b54 00021354 00021354 0 00000000 6026641-008_(size3_5_production_bootloadable).bin

.text 00023000 000bb080 00001b60 00023000 00023000 251 00003000 6026641-008_(size3_5_production_bootloadable).bin

.sdata2 000de080 00000570 000bcbe0 000de080 000de080 38555 000be080 6026641-008_(size3_5_production_bootloadable).bin

.sbss2 000de5f0 00000010 000bd150 000de5f0 000de5f0 0 000be5f0 6026641-008_(size3_5_production_bootloadable).bin

extab 000de600 000034e0 000bd150 000de5f0 000de5f0 38625 000be5f0 6026641-008_(size3_5_production_bootloadable).bin

extabindex 000e1ae0 00004f70 000c0630 000e1ad0 000e1ad0 39302 000c1ad0 6026641-008_(size3_5_production_bootloadable).bin

.funcInRam 20000000 000000b0 000c55a0 000e6a50 000e6a50 40319 000c6a50 6026641-008_(size3_5_production_bootloadable).bin

.data 200000b0 00019d80 000c5650 000e6b00 000e6b00 40328 000c6b00 6026641-008_(size3_5_production_bootloadable).bin

.sdata 20019e30 000007ac 000df3d0 00100880 00100880 45621 000e0880 6026641-008_(size3_5_production_bootloadable).bin

.sbss 2001a5e0 00000d30 000dfb80 000e6a40 000e6a40 0 000c6a40 6026641-008_(size3_5_production_bootloadable).bin

.bss 2001b310 0011ee34 000dfb80 000e6a40 000e6a40 0 000c6a40 6026641-008_(size3_5_production_bootloadable).bin

.PPC.EMB.sdata0 2013a144 00000000 000dfb80 000e6a40 000e6a40 0 00000000 6026641-008_(size3_5_production_bootloadable).bin

.PPC.EMB.sbss0 2013a144 00000000 000dfb80 000e6a40 000e6a40 0 00000000 6026641-008_(size3_5_production_bootloadable).bin

.identity 00022008 00000008 000dfb80 00022008 00022008 250 00002008 6026641-008_(size3_5_production_bootloadable).bin

.variables 40000000 000059f8 000dfb88 00101030 00101030 45720 000e1030 6026641-008_(size3_5_production_bootloadable).bin

.__CodeSys_ram 4000f800 00000014 000e5580 00106a28 00106a28 46872 000e6a28 6026641-008_(size3_5_production_bootloadable).bin

.PPC.EMB.apuinfo 001c783c 00000000 002acdd0 002ae27c 002ae27c 0 00000000 6026641-008_(size3_5_production_bootloadable).bin

.debug_abbrev 000001e5 000e5594

.debug_info 000ad1f4 000e5779

.debug_aranges 00000080 0019296d

.debug_line 0008ca0e 001929ed

.debug_loc 0003d193 0021f3fb

.debug_pubnames 0000e22a 0025c58e

*************************************************

I am not sure who to get rid of these warnings, or why my code is not running correctly. It simply loads PC with internal RAM address and then hangs there.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

It seems to me that lcf file is valid and no linker section overlap warning should be generated for sbss2 section.

Which version of CodeWarrior are you using?

There was an issue with an overlap message when sdata2/sbss2 section moved from RAM into Flash for an older version of CodeWarrior for MPC55xx/56xx v2.x.

I'd recommend you to check with the latest available compiler (CodeWarrior for MCUs v11 - compiler version 4.3.315)

Attached are the compiler release notes.

Hope it helps.

Stan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stan,

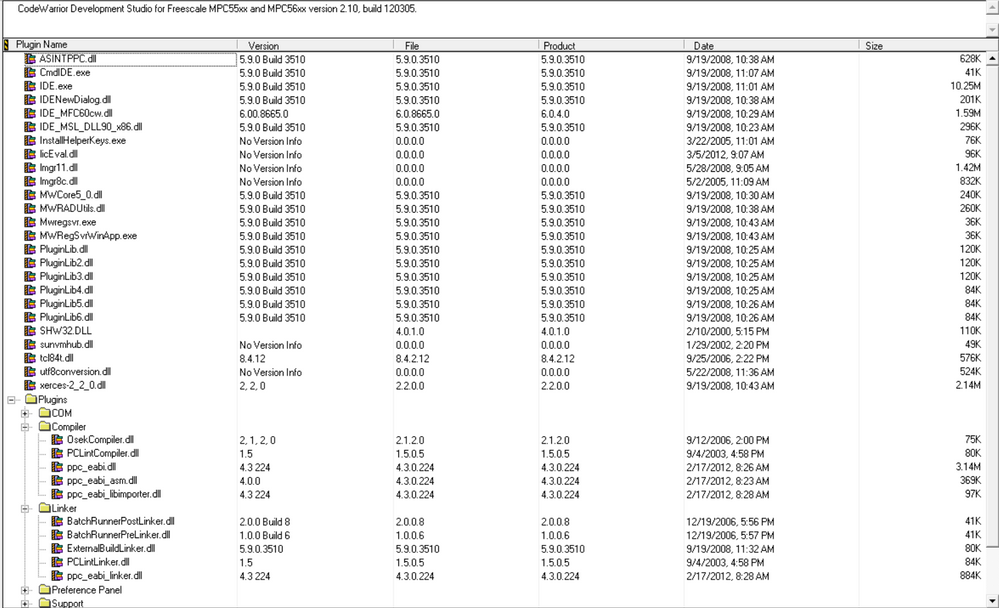

I am using CW version 5.9, I guess this is the latest supported version for the my controller, if you can confirm it will be great help. I am using mpc5553. please refer below snap for the Code Warrior, compiler and linker details,

If this is not the correct one, IS there anyway I can update the linker/compiler in the same CW version? or do i need to install the CodeWarrior for MCUs v11?

Thanks,

Mohammed

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mohamed,

Thanks for the update.

Sorry I haven't noticed you are targeting MPC5553.

Indeed MPC55xx is supported by CodeWarrior for MPC55xx/56xx v2.10 which you already have.

It is possible to use just the build tools (compiler, assembler and linker) form CodeWarrior for MCUs v10.X+ but it would require converting the IDE project into makefile one.

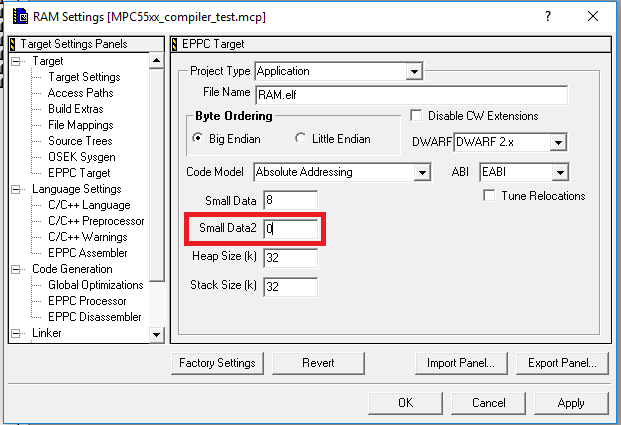

You might rather try to either disable small data section 2 generation:

or try to move .sdata2 .sbss2 into RAM instead of Flash.

Hope it helps.

Stan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stan,

thanks for the suggestions, I tried all but no luck yet, can you direct some more pointers please?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have asked my colleague to check this because he is more experienced in this area. I hope we will hear from him soon.

Regards,

Lukas