- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: MK20 digital input impedance

MK20 digital input impedance

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MK20 digital input impedance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, I'm coming on Kinetis forum, because I got an issue I couldn't explain an MK20DX256, here are messages I've posted about this issue :

- https://electronics.stackexchange.com/questions/311255/input-leakage-on-digital-input

- https://forum.pjrc.com/threads/44907-Teensy-3-2-Input-impedance?p=146096

I'm coming here, because I did not get any precise anwswers about issue described below.

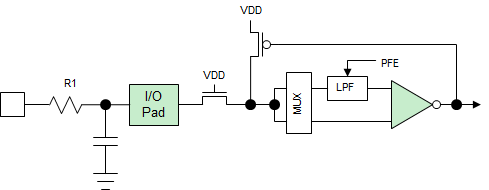

To sum up, I'm using MK20DX256. Recently I got a input impedance problem. When trying to read jack status using this circuit

using a GPIO configured as digital input I read 3.3V and ~1.4V, when jack is connected / disconnected, it should be 3.3V ~ 0.3V. I solved it using a voltage follower.

But from datasheet p 15/16 , I cannot understand why do I have some such leakage current. So, here are my questions :

- when jack is not connected, voltage output on jack detector (when MK20 not connected) circuit is ~0.3V with an impedance of 60k. If I get 1.4V on input of mk20 when I connect this circuit, that means on MK20 a 100k input impedance is present. Why such an impedance, when in datasheet when Vss <= Vin <= Vil, typical leakage current is 0.002µA?

- leakage is because of input protection leakage (also refer datasheet p41), but my question is why at Vdd, leakage decreases so much, when in theory it increases with voltage for a diode. Leakage current in this zone is 1µA (max 50µA) << leakage in Vil < Vin < Vdd zone. It must ne because of 5V input protection, but could you detail precisely how it is done internally?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

There is a document about Kinetis hardware design Tip & Tricks, please check below link for detailed info:

Kinetis Hardware Design Tip & Tricks

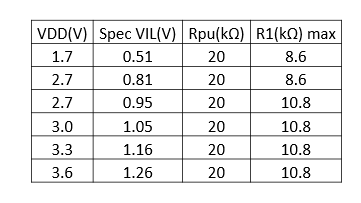

On pins wiTh 5V ToleranT inpuTs, Too large oF a pull-down resisTor can end up wiTh >10ua leakage currenT.

Please see The datasheet for maximum resistance value allowed.

If R1 is too high, the pin level will not drop below VIL which is needed to turn off the p-channel keeper.

R1 must be low enough such that the PFET current will make this IR less than VIL when signal is grounded

Use 20uA to calculate initial R1 value & pick lower value

VDD(V) | Spec VIL(V) | R1(kΩ) max |

1.7 | 0.51 | 25.5 |

2.7 | 0.81 | 40.5 |

2.7 | 0.95 | 47.3 |

3.0 | 1.05 | 52.5 |

3.3 | 1.16 | 57.8 |

3.6 | 1.26 | 63.0 |

If using the internal Pull-up resistor (20kΩ to 50kΩ), Use min Rpu value to calculate initial R1 value & pick lower value:

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your precise response. Just a last thing, I did not find in datasheet given values, can you give me the good datasheet link?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That's a pity.

I checked the MK20 latest datasheet without related info. Sorry for the inconvenience may cause.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------