- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- New KL25Z sample reset pin has 125KHz output

New KL25Z sample reset pin has 125KHz output

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Because I can not connect my CMSIS-DAP to custom KL25Z boards, (Check this thread: https://community.freescale.com/message/380989#380989) which has brand new sample ordered via element14.com. I probes the reset pin after getting suggestions from pgo

According to KL25P80M48SF0RM.pdf, $6.2.2.1 External pin reset

This pin is open drain and has an internal pullup device. Asserting RESET wakes the device from any mode.

The RESET pin can be disabled by programming RESET_PIN_CFG option bit to 0. When this option selected, there could be a short period of contention during a POR ramp where the device drives the pin out low prior to establishing the setting of this option and releasing the RESET function on the pin.

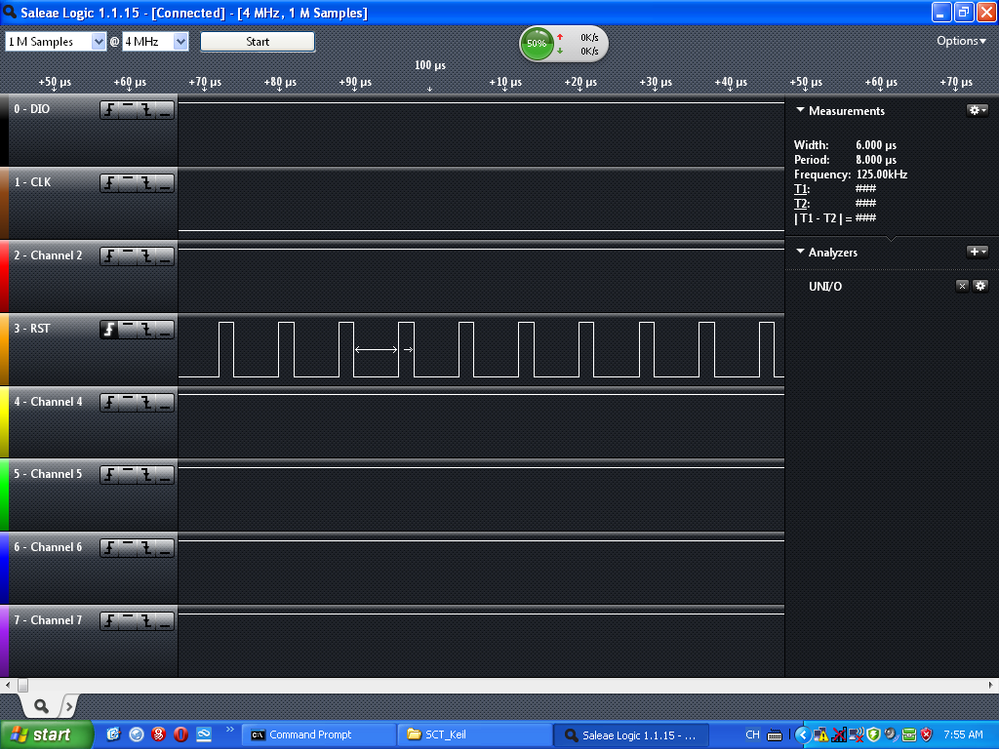

I got the a wave from reset pin, about 125KHz, That means the KL25Z is always in reset pin.

Here come my questions:

- Is it normal to a new sample?

- Does it apply to KL only or all Kinetis (K+KL)?

- How to solve it and download my code?

UPDATE

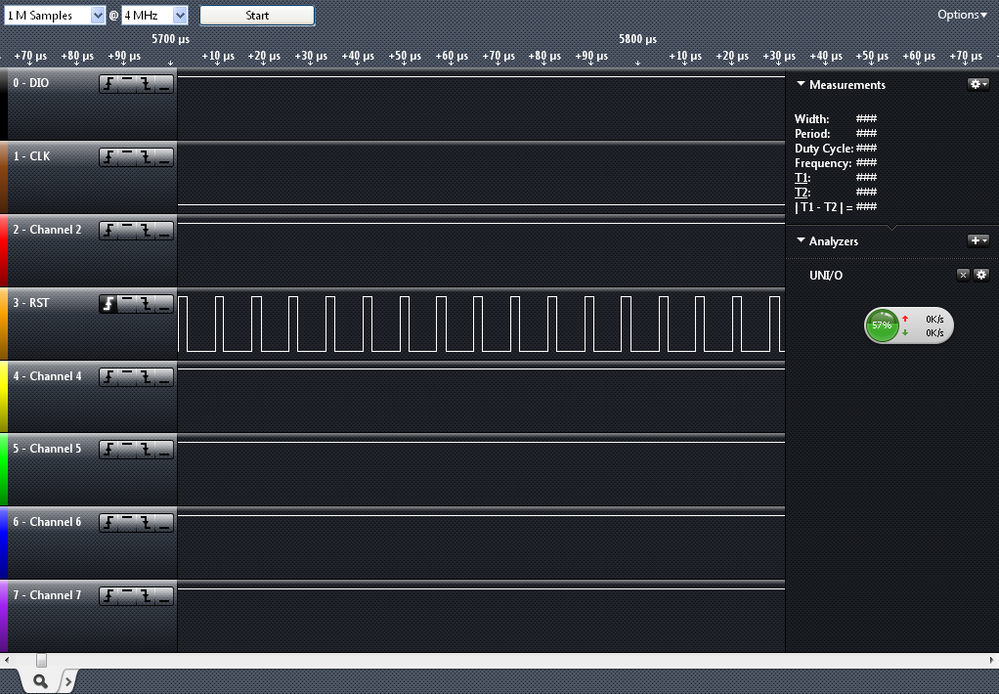

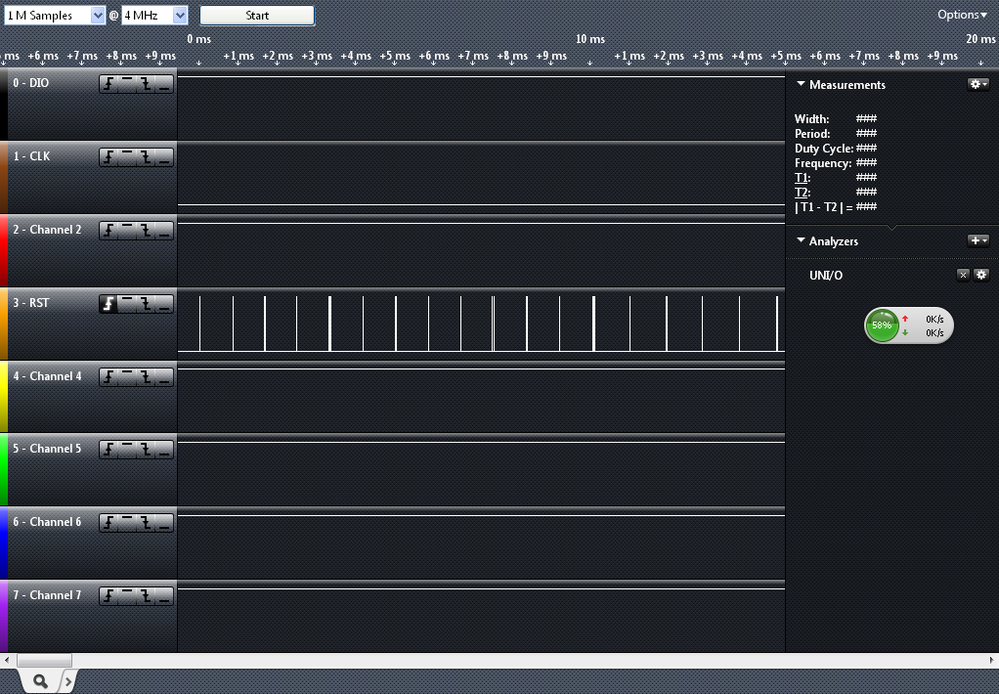

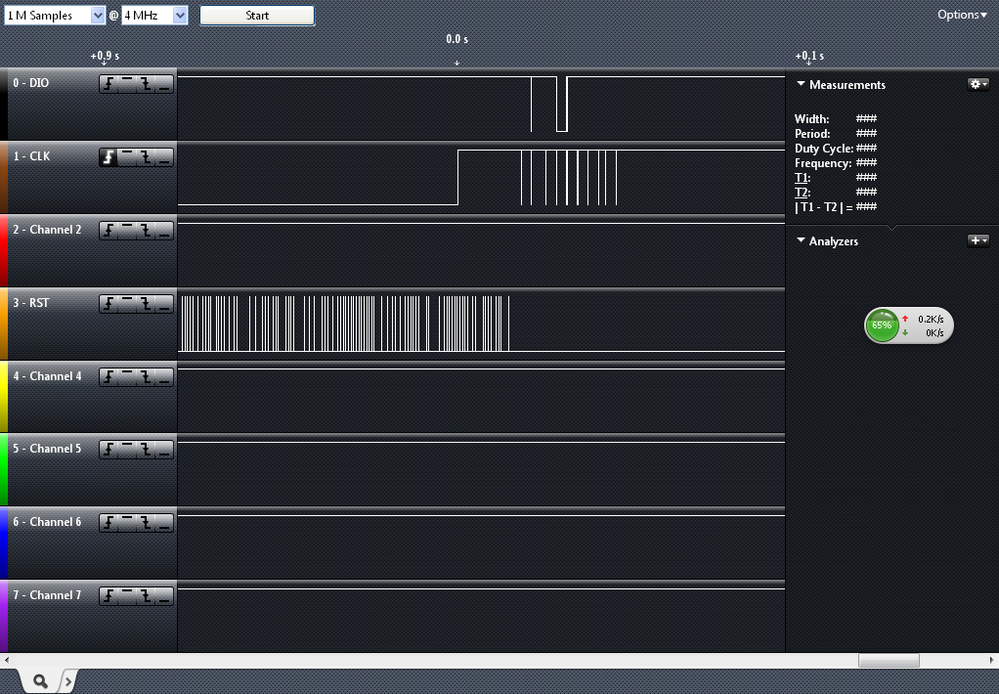

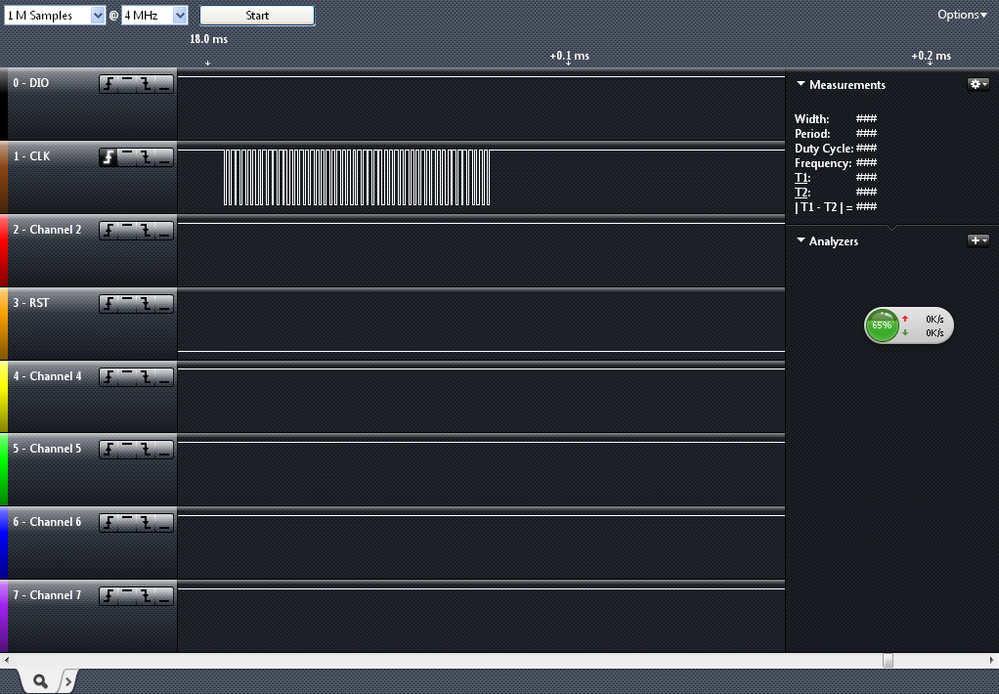

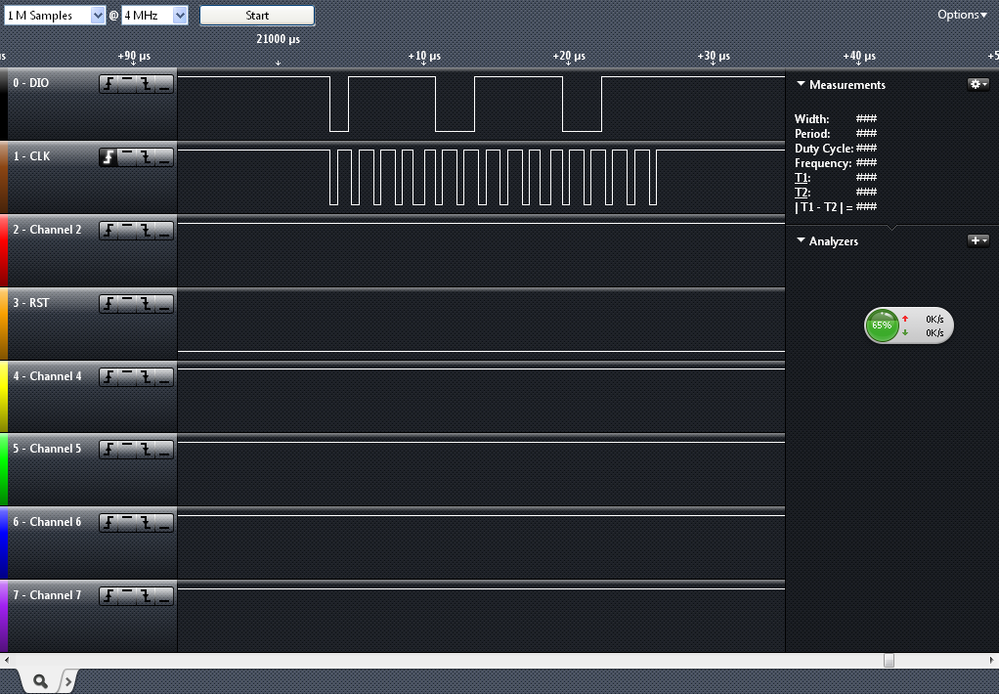

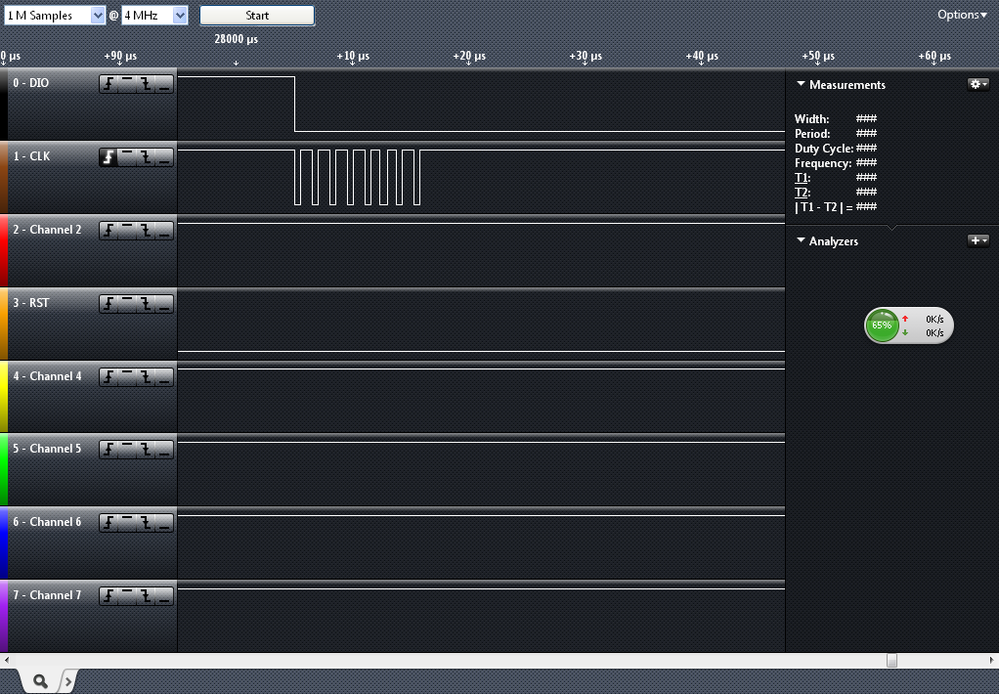

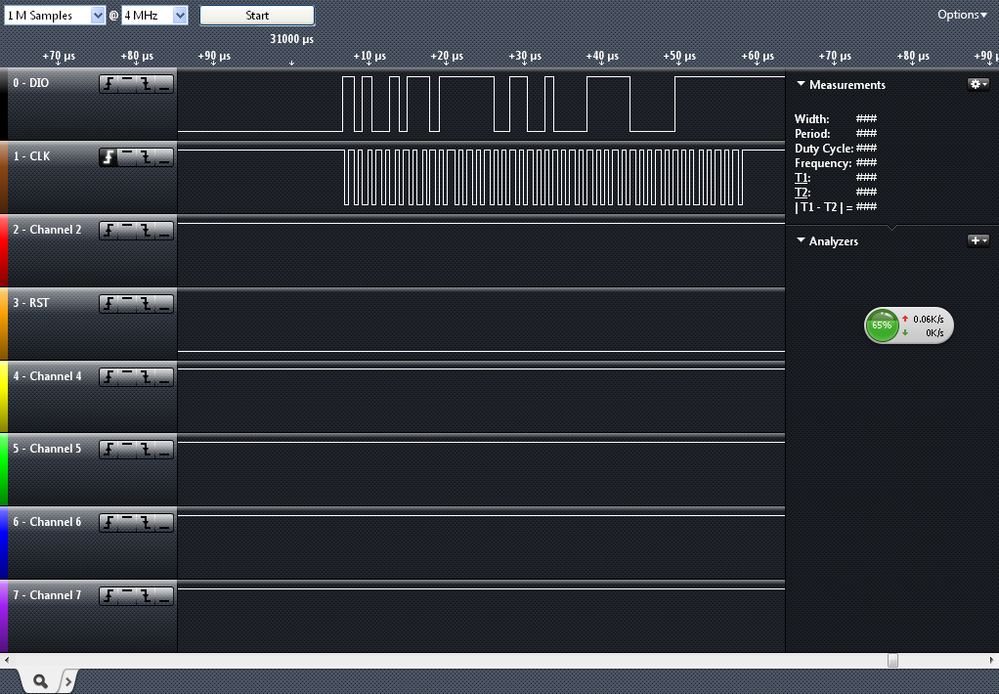

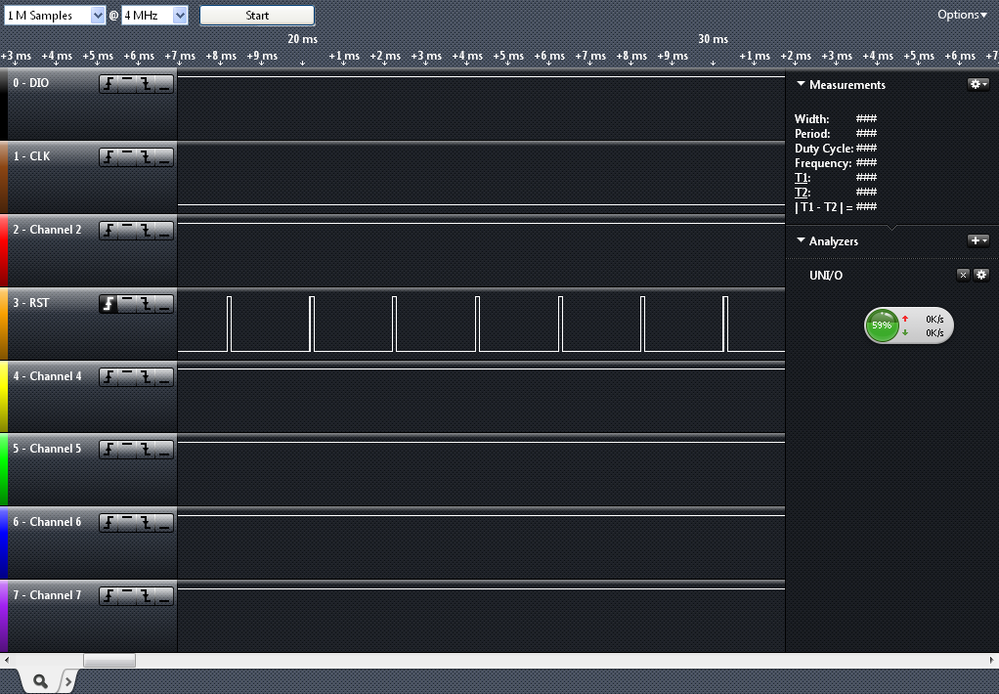

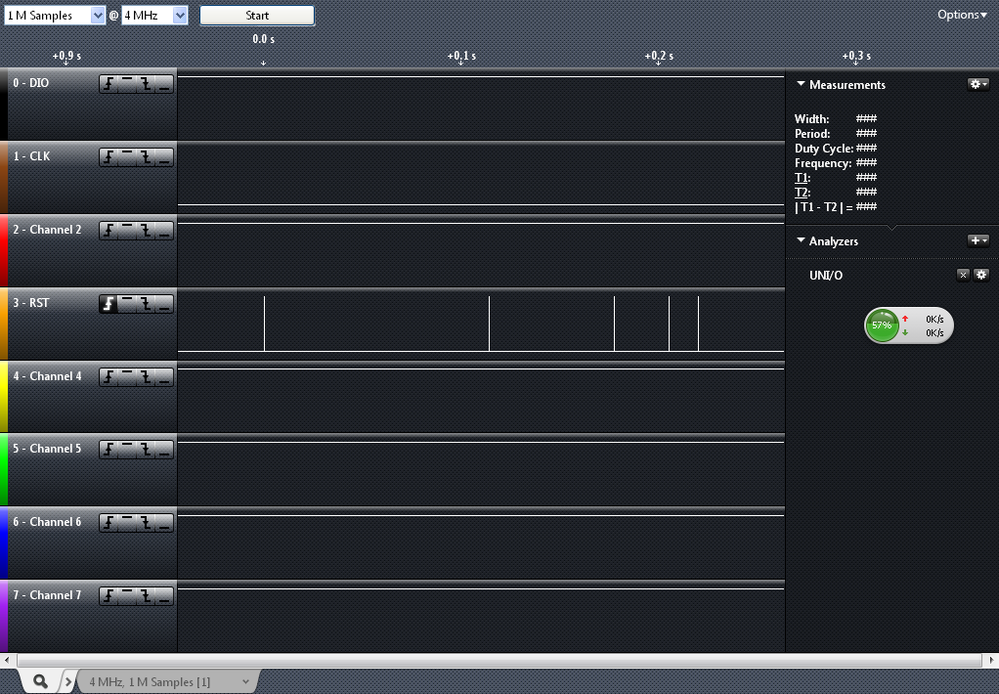

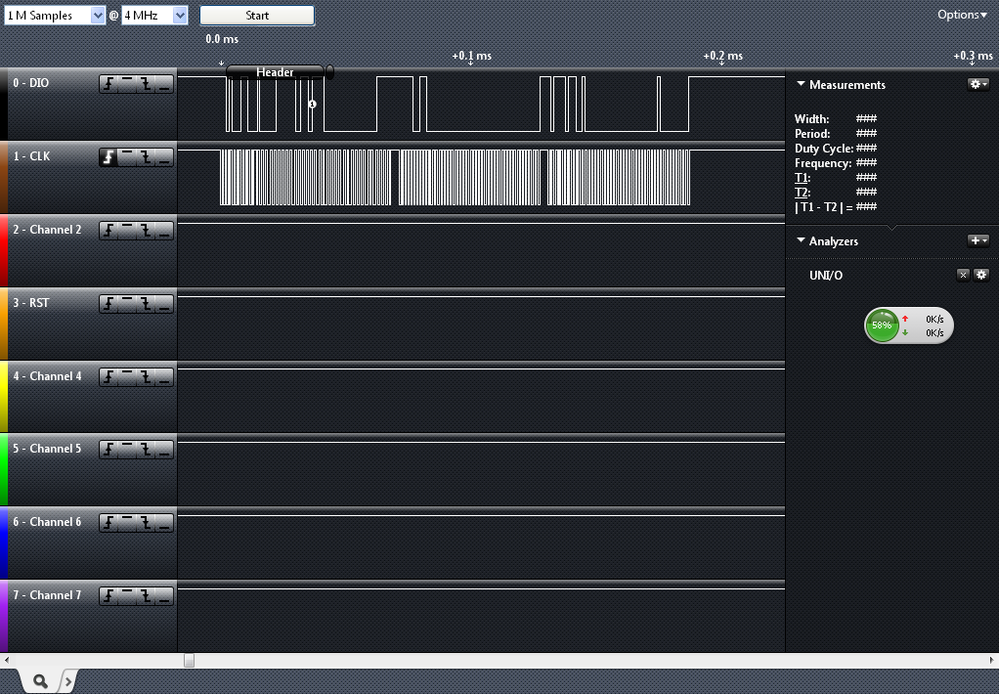

As a cross check, I post some screenshots from my LogicScope.

Fig 1: New KL25Z samples without connecting to SWD debugger

Fig 2: New KL25Z sample connecting to SWD debugger

Fig 3. New KL25Z trying to connect to SWD (There are three attepts to talk to the KL25Z on DIO/CLK, which keeps LOW for a while on DIO)

Fig 4. Zoom in A (CLK pulses)

Fig 5. Zoom in B

Fig 6. Zoom in C

Fig 7. Zoom in D

Fig 8. FRDM on board KL25Z erased disconnected to OpenSDA

Fig 9. FRDM on board KL25Z erased connected to OpenSDA

Fig 10. FRDM on board KL25Z programmed by OpenSDA

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well. Good news for this thread. It has nothing to do with RESET pin.

I added a series resistor (220R) to SWD_CLK, then most of the debuggers can talk to KL25Z now.

Yes, it is a hardware issue caused by PCB layout as well as IC pin layout, maybe.

Now I can move on to my next project.

What's the minimum circuit requirement for KL/K mcu programming?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well. Good news for this thread. It has nothing to do with RESET pin.

I added a series resistor (220R) to SWD_CLK, then most of the debuggers can talk to KL25Z now.

Yes, it is a hardware issue caused by PCB layout as well as IC pin layout, maybe.

Now I can move on to my next project.

What's the minimum circuit requirement for KL/K mcu programming?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The 125KHz output is not a question anymore. However I will not close that since I am share of picking "correct answer" option to close it.

Any comments are still welcome.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kai,

As described in the quoted thread - This is to be expected with a blank (new) chip.

I have observed this with a range of Kinetis devices including newly purchased chips.

I am unsure why none of the programmers you have tried can cope with this or even if this is the cause of your problems.

Since this tends to be the usual case with a blank chip, and usually the programmers cope with it, the problem may lie somewhere else.

bye

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to the screenshot, at least the connections are correct: SWD_DIO is internally pull high, SWD_CLK is internally pull low, and RST pin is connected as well. And obviously power and ground are connected well.

Sorry, I used to think that is unexpected performance of a blank chip. Since FTFA_FOPT should be 0xFF, and RESET_PIN_CFG should be "1", which means a dedicated reset pin.

I will probe on board KL25Z in FRDM and the one on our board as cross checking.