- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors Knowledge Base

- :

- i.MX6SL EPDC QoS

i.MX6SL EPDC QoS

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

i.MX6SL EPDC QoS

i.MX6SL EPDC QoS

Why raising QoS priority for EPDC

Eink has been developing higher resolution panel. With higher resolution, TCE underrun problem is observed more easily. Highest QoS priority can provide obvious improvement.

What's TCE underrun

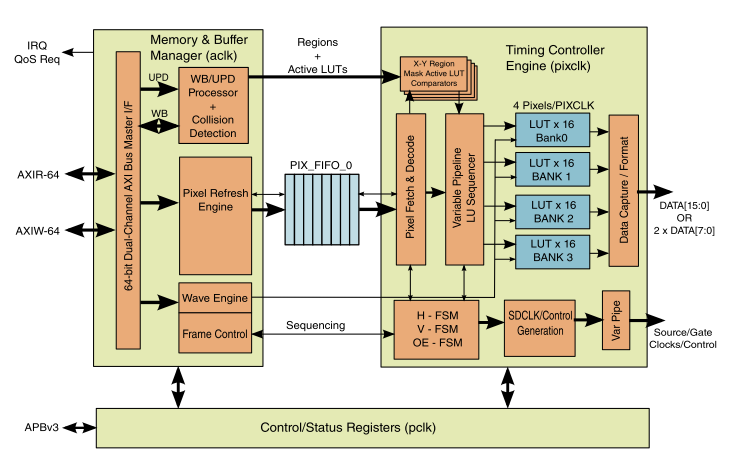

TCE is Timing Controller Engine which is responsible for TFT scan frame refreshes. The pixel FIFO (PIX_FIFO) is used to load working buffer pixel data for TCE. When FIFO underrun, TCE_UNDERRUN_IRQ interrupt is triggered, and TCE underrun log pops up in kernel log.

The pixel data is processed by TCE to generate TFT voltage control pixels for panel. If an underrun occurs, unknown data is used and that can damage the panel.

About the patch

The patch raises EPDC reading to highest priority (QoS='f'), so the EPDC reading becomes real time channel in MMDC configuration. The patch is based on L4.1.15 kernel. Stress test of unit test can pass with 1920x1440 configuration.