- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape Knowledge Base

- :

- Flash layout for new boot flow with TF-A

Flash layout for new boot flow with TF-A

Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

Flash layout for new boot flow with TF-A

Flash layout for new boot flow with TF-A

Please note that the LSDK memory layout for TF-A boot flow explained in this topic is only applicable for LSDK 18.12 and newer releases.

The following table shows the memory layout of various firmware stored in NOR/NAND/QSPI flash device or SD card on all QorIQ Reference Design Boards.

When the board boots from NOR flash, the NOR bank from which the board boots is considered as the "current bank" and the other bank is considered as the "alternate bank". For example, if LS1043ARDB boots from NOR bank 4, to update an image on NOR bank 0, you need to use the "alternate bank" address range,0x64000000 - 0x64F00000.

| Firmware Definition | MaxSize | Flash Offset (QSPI/NAND flash) | Absolute address (NOR bank 0 on LS1043ARDB, LS1021ATWR) | Absolute address (NOR bank 4 LS1043ARDB, LS1021ATWR) | Absolute address (NOR bank 0 on LS2088ARDB) | Absolute address (NOR bank 4 on LS2088ARDB) | SD Start Block No. | |

|---|---|---|---|---|---|---|---|---|

| RCW + PBI + BL2 (bl2.pbl) | 1 MiB | 0x00000000 | 0x60000000 | 0x64000000 | 0x580000000 | 0x584000000 | 0x00008 | |

| ATF FIP Image (fip.bin) BL31 + BL32 + BL33 | 4 MiB | 0x00100000 | 0x60100000 | 0x64100000 | 0x580100000 | 0x584100000 | 0x00800 | |

| Boot firmware environment | 1 MiB | 0x00500000 | 0x60500000 | 0x64500000 | 0x580500000 | 0x584500000 | 0x02800 | |

| Secure boot headers | 2 MiB | 0x00600000 | 0x60600000 | 0x64600000 | 0x580600000 | 0x584600000 | 0x03000 | |

| Secure header or DDR PHY FW | 512 KiB | 0x00800000 | 0x60800000 | 0x64800000 | 0x580800000 | 0x584800000 | 0x04000 | |

| Fuse provisioning header | 512 KiB | 0x00880000 | 0x60880000 | 0x64880000 | 0x580880000 | 0x584880000 | 0x04400 | |

| DPAA1 FMAN ucode | 256 KiB | 0x00900000 | 0x60900000 | 0x64900000 | 0x580900000 | 0x584900000 | 0x04800 | |

| QE/uQE firmware | 256 KiB | 0x00940000 | 0x60940000 | 0x64940000 | 0x580940000 | 0x584940000 | 0x04A00 | |

| Ethernet PHY firmware | 256 KiB | 0x00980000 | 0x60980000 | 0x64980000 | 0x580980000 | 0x584980000 | 0x04C00 | |

| Script for flashing image | 256 KiB | 0x009C0000 | 0x609C0000 | 0x649C0000 | 0x5809C0000 | 0x5849C0000 | 0x04E00 | |

| DPAA2-MC or PFE firmware | 3 MiB | 0x00A00000 | 0x60A00000 | 0x64A00000 | 0x580A00000 | 0x584A00000 | 0x05000 | |

| DPAA2 DPL | 1 MiB | 0x00D00000 | 0x60D00000 | 0x64D00000 | 0x580D00000 | 0x584D00000 | 0x06800 | |

| DPAA2 DPC | 1 MiB | 0x00E00000 | 0x60E00000 | 0x64E00000 | 0x580E00000 | 0x584E00000 | 0x07000 | |

| Device tree(needed by uefi) | 1 MiB | 0x00F00000 | 0x60F00000 | 0x64F00000 | 0x580F00000 | 0x584F00000 | 0x07800 | |

| Kernel | lsdk_linux.itb | 16 MiB | 0x01000000 | NA | NA | NA | NA | 0x08000 |

| Ramdisk rfs | 32 MiB | 0x02000000 | NA | NA | NA | NA | 0x10000 | |

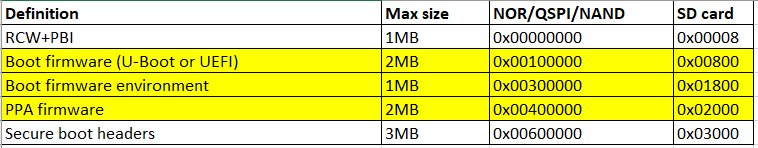

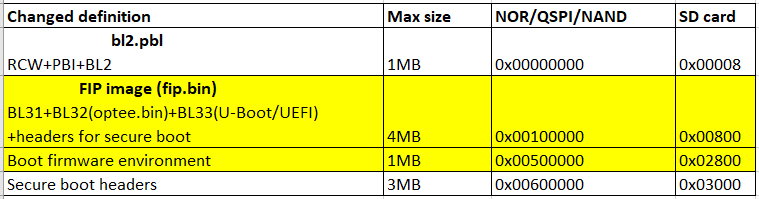

The following figures highlight the changes in the flash layout for previous boot flow (with PPA) and flash layout for TF-A boot flow.

Flash layout for previous boot flow (with PPA)

Changed flash layout for TF-A boot flow

No ratings