- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- University Programs

- :

- University Programs Knowledge Base

- :

- MCU 101: Pulse Width Modulation

MCU 101: Pulse Width Modulation

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

MCU 101: Pulse Width Modulation

MCU 101: Pulse Width Modulation

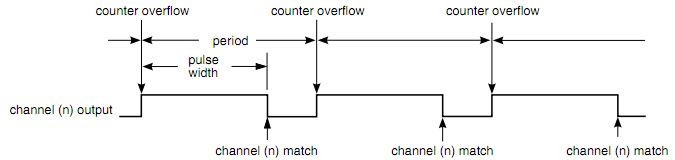

Pulse-width modulation (PWM), is a technique utilized in robotics for controlling motors and servos. Through the use of internal counters, the microcontroller modulates the duty cycle of a square wave to control the amount of power delivered to a device. The Duty Cycle referes to the porportion of time the square wave is 'on' as compared to the repeating signal period. The higher the duty cycle the higher the power carried in the signal. Duty cycle is expressed as a percentage of time the signal is 'on', with 100% being consistently on.

Configuring the Timer

The generation of a PWM signal using is based on hardware comparisons between register values and free running hardware counters. The timer module offers similar hardware comparison in the form of output compare circuitry. The contents of a register are continually compared to the master free-running timer. When a match occurs, a hardware output event can be configured to take place and an interrupt can then call a service routine.

Timer I/O

The Timer I/O port control registers are located in the Port Integration Module (PIM). Each port can be configured on a pin-by-pin basis and each timer input capture/output compare channel is associated with a single pin. On reset, timer modules are disabled and the appropriate I/O port defaults to a high impedance input. The initial state of a pin can be defined by configuring the appropriate general purpose I/O pin as an output in the Data Direction Register (DDRT) and writing the Port Data Register (PTx) to the appropriate state. An external pull device is required to control the level during reset.Setting the Timer Enable (TEN) bit in the Timer System Control Register (TSCR1) enables the timer module. The output compare functionality is disabled in the default module reset state. In this mode, the Data Direction bits (DDRTx) control the I/O state of the pins while the Input Compare logic monitors transitions on the pins. Setting the appropriate bit in the Timer Input Capture/Output Compare Select (TIOS) register enables a timer channel for output compare, as needed for PWM generation. In output compare mode, the Output Mode (OMn) and Output Level (OLn) bits in the Timer Control Registers (TCTL1/2) simultaneously select the compare event action and enable the connection of the output compare output logic to the relevant pin. If the OMn:OLn control bits for a channel are both zero the DDRTx and PTx bits control the state of the I/O pin. Setting either (or both) of the OMn:OLn bits connects the output compare circuitry to the pin, over-riding the DDRTx and PTx settings. Following a reset, the output state for each output compare circuit is zero.

For PWM generation, the OM bit is set (= 1) so that the output compare output follows the state of the associated OL bit on each compare event. The state of the OL bit is inverted every time the timer channel interrupt is serviced to produce a toggling output. Clearing or setting the TEN bit disables or enables the timer module respectively, but does not modify the contents of any other timer control registers or the state of the output compare output logic

A number of considerations have to be made when configuring the timer module for PWM. From a high-level point of view, the main considerations are:

• PWM Frequency

• PWM Duty Cycle

In order to generate the required PWM frequency, the bus clock frequency must be known, and the timer prescaler must be set. These values will depend on the range of PWM frequencies that will be generated and the degree of resolution of the PWM signal. Maximum resolution and PWM frequency are limited by the maximum timer clock frequency. Lower PWM frequencies are limited by the minimum timer clock frequency. This can sometimes result in a trade-off and can be evaluated as shown in Figure 1.

Once the timer channel is configured, the PWM signal can be generated using the timer channel interrupt. This should be configured to call an interrupt service routine (ISR) to load the timer compare register with the appropriate compare value (mark or space). This is achieved by identifying whether the last action was a negative or a positive edge transition, switching the transition status and loading the compare register

with the next appropriate value. References to the master timer count register can be avoided by simply adding consecutive mark and space values to the timer compare register on successive ISR function calls as shown in Figure 3. Timer roll-over is seamless when using unsigned integer addition. Using the previous compare value as a reference for generating the next compare value allows precise output timing even though the ISR latency may vary.

Starting the PWM is a task that requires careful consideration. In order to start the PWM generation using the interrupt, it is necessary to configure the first compare event manually. It is necessary to configure a forced compare by setting a compare to switch the output pin to the first transition state. After the initial compare event, interrupts will handle the PWM generation. The HCS12 does not support hardware forced compare, but a forced compare can be configured by setting a normal compare a few cycles ahead of the current free-running timer value. The cycles are necessary to compensate for internal latency within the MCU. The number of cycles will vary depending on the core and module clocks. When stopping the PWM generation, it is important to consider runt pulses (pulses with width shorter than the prescribed mark or space ratio as appropriate). To avoid these pulses, disable the PWM generation by setting the appropriate local interrupt mask within the associated interrupt service routine. The appropriate state of the pin at stop time can be set by disabling the interrupt in either part of the ISR; either the rising

or falling edge portion.