- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- NXP Tech Blogs

- :

- NXP Tech Blog

- :

- LPC5500 MCU Series: There's a lot under the hood (Part 3 of 3) - SCT, "Programmable Logic" and Boot ROM

LPC5500 MCU Series: There's a lot under the hood (Part 3 of 3) - SCT, "Programmable Logic" and Boot ROM

LPC5500 MCU Series: There's a lot under the hood (Part 3 of 3) - SCT, "Programmable Logic" and Boot ROM

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

I recently wrote about the ample processing capabilities built into the LPC55S69 MCU in addition to the Dual USB capabilities and large banks of RAM. Now it is time to explore some peripherals and features that are often overlooked in the LPC family but are very beneficial to many embedded system designs.

The State Configurable Timer

An absolute gem in the LPC family is the “State Configurable Timer” (SCT). It has been implemented in many LPC products and I feel is one of the most under-rated and often misunderstood peripherals. When I first encountered the SCT, I wrote it off as a “fancy PWM” unit. This was a mistake on my part as the SCT is an extremely powerful peripheral that can solve many logic and timing challenges. I have personally been involved in several design efforts where I could remove the need for an additional programmable logic device on a PCB by taking advantage of the SCT in an LPC part. At its core, the SCT is a up/down counter that can be sequenced with up to 16 events. The events can be triggered by IO or by one of 16 possible counter matches. An event can then update a state variable, generate IO activity (set, clear, toggle), or start/stop/reverse the counter.

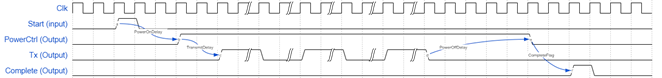

Consider an example which is similar to a design problem I previously used the SCT for.

Given a 1 cycle wide Start input signal

i.) Assert a PowerCtrl signal on the 3rd Clk cycle after the start.

ii.) After 2 Clk cycles the assertion of PowerCtrl, output exactly 2 pulses on the Tx output pin at a programmable period.

iii.) 5 Clk cycles after ii.), de-assert PowerCtrl

iv.) After 2 Clk cycles of the de-assertion of PowerCtrl, output a 1 cycle pulse to the Complete pin.

This task could be done in pure software if the incoming CLK was slow enough. Most timer/counter units in competing MCUs would not be able to implement this particular set of requirements In my use case (an acoustic transmitter), I was able to implement this completely in the SCT with minimal CPU intervention and no external circuitry. This is a scenario where I might consider an external CPLD or FPGA but the SCT would be more than capable of implementing the behavior. I highly recommend grabbing the manual for the LPC55 family and read chapter 24. If you have never used a peripheral like the SCT, I highly recommend learning out about it.

Programmable Logic Unit

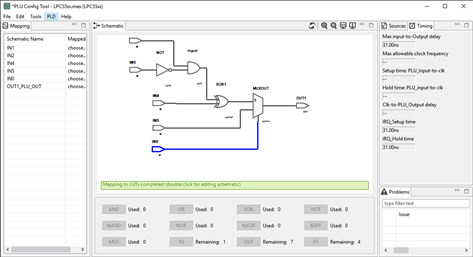

In addition to the SCT, there is a small amount of programmable logic in the LPC55 family. The PLU is an array of twenty 5-input Look up tables (LUTs) and four flip-flops. From the external pins of the LPC55xx, there are 6 inputs to the PLU fabric and 8 outputs. While this is not a large amount of logic, it is certainly enough to replace some external glue logic you might have in your design. There is even a free tool to draw your logic schematically or describe using the Verilog HDL.

I often find I need a just handful of gates in a design to glue a few things together and the PLU is the perfect peripheral for this need.

LPC Boot ROM

Another indispensable feature that has been in the LPC series since the beginning is a bootloader in ROM. For me, it is a must have as it means I can program/recover code via one of many interfaces without a JTAG/SWD connection. For factory/production programming and test, it saves quite a bit of hassle. The boot rom allows device programming over SPI, UART, I2C or UART. I typically use the UART or USB interface with FlashMagic. This feature has certainly benefited me on *every* embedded project, especially when it comes to production programming and test. There have even been some handy times to recover a firmware image in field. Many designs included some sort of bootloader and having an option that is hard coded in ROM is a great benefit that you get for free in the LPC family.

It is difficult to capture all the benefits of the new LPC55 family, but we hope you are interested. The LPC55 family is offered many convenient IC packages, is low power (both active and sleep) and is packed with useful peripherals. The LPC55S69 development board is available at low cost. Combining the low cost hardware tools with the MCUXpresso SDK, you can start LPC55 development today. From here we are going to start looking at some interesting how-to’s and application examples with the LPC55 family. Stay tuned and visit www.nxp.com/LPC55S6x to learn more.

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.

-

101

7 -

Automotive Ethernet

3 -

communication standards

12 -

General Purpose Microcontrollers

35 -

i.MX RT Processors

54 -

i.MX Processors

85 -

Interface

14 -

introduction

32 -

LPC Microcontrollers

73 -

MCUXpresso

47 -

MCUXpresso Secure Provisioning Tool

1 -

MCUXpresso Conig Tools

31 -

MCUXpresso IDE

53 -

MCUXpresso SDK

38 -

MCX

19 -

Model-Based Design Toolbox

6 -

Motor Control

7 -

MQX Software Solutions

2 -

PMIC

12 -

QorIQ Processing Platforms

1 -

QorIQ Devices

8 -

S32N Processors

5 -

S32Z|E Processors

7 -

Security

15 -

Sensor

6 -

SW | Downloads

22 -

Technology Focus

26 -

日本語ブログ

97

- « Previous

- Next »