- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- iMXRT1064: clock configurations for PLL2 PFD0

iMXRT1064: clock configurations for PLL2 PFD0

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

iMXRT1064: clock configurations for PLL2 PFD0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We are using a i.MX RT controller for eMMC application development.

we are facing some clock related issues for USDHC driver as below

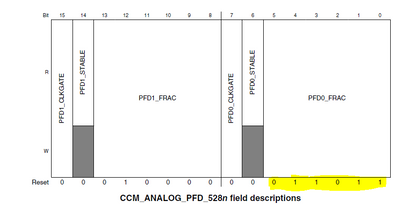

a) What should be the reset value of PFD0_FRAC parameter in register CCM_ANALOG_PFD_528n ?

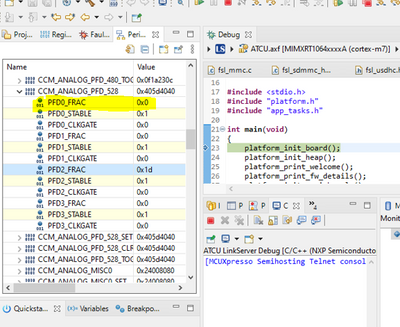

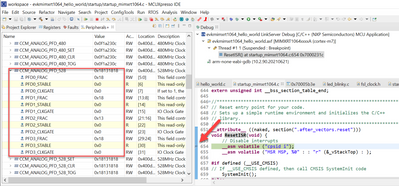

Observations: after power on the MCU before any system / clock initializations, we have read the CCM_ANALOG_PFD_528n register value in debug mode and get the value of PFD0_FRAC = 0 (000000b) but as per datasheet reset value of this field should be 0x1B.(011011b)

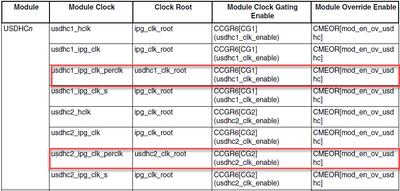

b) As per IMXRT1064RM (reference manual) document, base clock for the SDCLK frequency generation is ipg_perclk, but in example driver code for SDMMC, USDHC_CLK_ROOT is used to derive SDCLK frequency. Should we consider ipg_perclk or USDHC_CLK_ROOT for SDCLK configurations.

Thanks,

Deep D.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

a) a) What should be the reset value of the PFD0_FRAC parameter in register CCM_ANALOG_PFD_528n?

-- The reset value of the PFD0_FRAC should be 0x0C, as it should be in the range of 12~35.

b) As per IMXRT1064RM (reference manual) document, base clock for the SDCLK frequency generation is ipg_perclk, but in example driver code for SDMMC, USDHC_CLK_ROOT is used to derive SDCLK frequency. Should we consider ipg_perclk or USDHC_CLK_ROOT for SDCLK configurations?

-- As the below figure shows, the ipg_clk_perclk is generated from the usdhcn_clk_root.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello jeremyzhou,

Thanks for the quick response.

a) -- The reset value of the PFD0_FRAC should be 0x0C, as it should be in the range of 12~35.

Yes, the range of PFD0_FRAC is from 12~15 , but as per reference manual reset value of this register should be 0x1b. (please refer screenshot of this register reset value from reference manual in above question).

Also, when we read this register value just after power on before clock initialization using debug mode, it is showing as 0x00. below is the screen shot of this register captured in debug mode at start up before clock initialization. (value of PFD2_FRAC is as per the reference manual)

b) -- As the below figure shows, the ipg_clk_perclk is generated from the usdhcn_clk_root.

In our project, ipg_clk_perclk is set to 75 MHz while usdhc1_clk_root is set to 198 MHz. In this case, which base frequency should be considered for clock generation of SDCLK.

Is there any specific application note available for USDHC driver, it would be really helpful to understand USDHC driver in more detail.

Thanks,

Deep darji

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

1) I've no idea with your screenshot, just as the below figure shows, the value of the CCM_ANALOG_PFD_528 conforms to the description of the RM.

2) Is there any specific application note available for USDHC driver, it would be really helpful to understand USDHC driver in more detail.

-- No, there's no similar application note.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------