- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MX RT クロスオーバーMCU

- :

- Re: i.mx rt 1062 SEMC DMA performance

i.mx rt 1062 SEMC DMA performance

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

i.mx rt 1062 SEMC DMA performance

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear sirs.

I try now interfacing imxrt1060<-->FPGA via SEMC SRAM interface with sync mode 16 bit multiplexed Addr/Data.

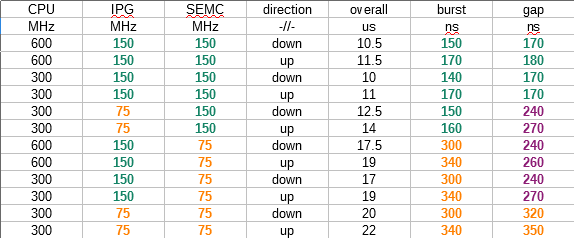

I use DMA transfer to/from FPGA and have a quite large time gaps between bursts in transfer.

My used parameters:

AXI and SEMC frequencies 150MHz

SEMC sync mode, latency=3, burst=4(->burst 16 words)

DMA transfer size 1 KB, DMA granularity 32 bytes;

All of this functionally works, I can write, read and check results. Time diagrams inside the each burst seems OK.

But overall transfer speed is more then 2-x less than expected.

We have this results (controlled by oscilloscope with CS pin):

150Mhz WR 1KB overall time=10us burst16 time=140ns gap time=170ns speed=102.4MBps

150MHz RD 1KB overall time=10.5us burst16 time=170ns gap time=170ns speed=97.5MBps

The best 1KB transfer time (in theory) must b:

32 {bursts} *(1{CS}+1{ADW}+3{latency}+16{burst}+1{/CS}+1{interval})*Tclk=4.9 us;

What causes our time gaps and how to eliminate/decrease it?

I attach a register dumps, captured just before DMA transfer launch, and ready to supply any other information if needed.

Thank you. Ivan.

PS:

I look at that threads for imx 6s, and can`t find any solution there...

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

@Hui_Ma I too am interested in this topic, do you have any update on access to the linked document above? thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

No answers several days, it`s sad...

I suspect, this problem can be a hardware restriction, I`d like to hear an answer from NXP support.

If I can do nothing to achieve expected peak throughput, I won`t waste my time on this.

Ivan.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Ivan,

Sorry for the later reply.

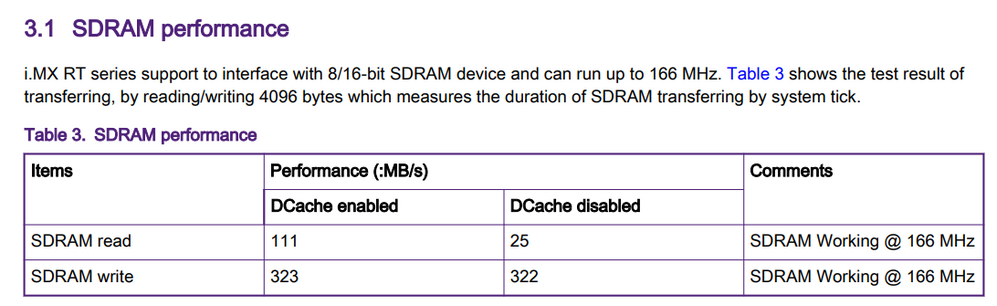

We don't have SEMC performance data for external FPGA, while we have SEMC SDRAM as a reference.

Please check AN12437 about SDRAM performance data.

SDRAM write performance better than read, for the write operation is pipelined.

For the DMA access could not enable DCache to increase Read performance, I think your test result is also reasonable.

Thanks for the attention.

best regards,

Mike

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks a lot, Mike.

There is a interesting picture in AN12437, I mark red the points which I use in my case (as I can understand):

Maybe, you could explain some things (or know someone, who can).

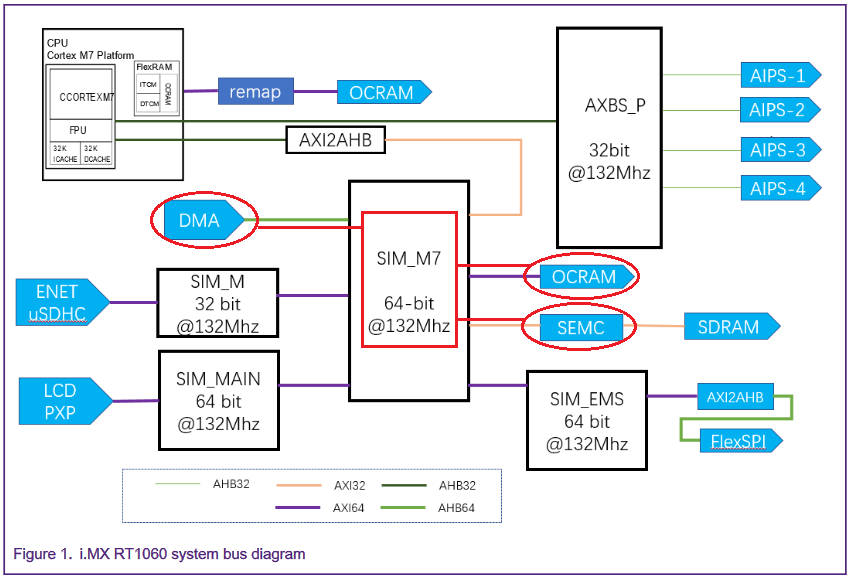

Lets speak, as an example, about DMA transfer from SEMC to OCRAM, the process can have a variants:

1. DMA reads 32bytes from SEMC via SIM_H7, and than writes 32bytes to OCRAM via SIM_H7

2. DMA organizes SEMC reading, OCRAM writing, and SIM_M7 converting between them.

i.e. reading and writing can be in parallel or sequential.

IF case #1 used, my time gaps are understandable. But doing such a loss of performance is so strange...

IF case #2, there are a chances to tune-up a process?

I can`t deal with only 50%, I want, at least, 80%.

Ivan.

P.S. I just now make a test with OCRAM<==>OCRAM DMA transfer (copy) 1 KB - time is 4us.

250 MBps copy = 500 MBps read + 500 MBps write (!!!).

It seems, no DMA engine, nor OCRAM connection are not a bottlenecks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Ivan,

SIM_M7 works as an arbitrator, which set access priority for masters (DMA, ENET, LCD and etc) to access Slave (OCRAM, SEMC connected external memory devices).

The working way is 1 as you listed:

1. DMA reads 32bytes from SEMC via SIM_H7, and than writes 32bytes to OCRAM via SIM_H7

So, there needs DMA to do read and write accessing.

There with the bandwidth difference for OCRAM and SEMC SDRAM:

Max. speed for OCRAM : 64bit 133MHz

Max. speed for SEMC SDRAM: 16bit 166MHz.

Thanks for the attention.

Have a great day,

Mike

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mike,

if we agree to previous, this does not explain, why gap time ( to act with relatively fast OCRAM) is equal or more then the (relatively slow)SRAM burst time. I do some measures about this. I vary CPU,IPG and SEMC frequencies and log the result time. Gap time depends on both IPG and SEMC clocks (violet).

My next questions maybe not to you personally, but to NXP support:

Can anybody please tell me, are this time gaps "normal" for this chip, or I can do anything to decrease them?

And, the second, is this performance drop the same in new RT 11xx series?

Thank you,

Ivan.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Ivan,

I would recommend to refer my colleague shared document about <iMXRTxxxx Memory Performance: ITCM / DTCM / OCRAM / SDRAM / FlexSPI (QSPI / HyperFLASH)> from here.

Wish it helps.

Have a great day,

Mike

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you Mike, but something goes wrong...

I can`t access this doc. Ivan.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Ivan,

I am checking with document author if that document could be shared.

I will update when I got any feedback.

best regards,

Mike

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Ivan,

That document is in preliminary status.

The author still need more time to edit before released.

While, I couldn't make sure when it will be released.

Sorry for that.

best regards,

Mike