- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- i.MXRT1176_flexspi_QSPI flash_quad mode abnormal operation

i.MXRT1176_flexspi_QSPI flash_quad mode abnormal operation

i.MXRT1176_flexspi_QSPI flash_quad mode abnormal operation

IMXRT1176 Controller was used, and mimxrt1170 evk board was customized and used.

IMXRT1176 Controller was used, and mimxrt1170 evk board was customized and used.

The problem is that Read and Write of the SPI method using D0 and D1 work, but Read and Write of Quad mode do not operate normally.

SPI Write -> SPI Read = normal operate

Quad Write -> Quad Read = Not operate

Quad Write -> SPI Read = Not operate

SPI Write -> Quad Read = some action (some error value output)

The connection of qspi flash is the same, (E14,F17,G14,F15,H15,H14,F16 / FlexSPI_A_DQS, FlexSPI_A_SS0, FlexSPI_A_CLK, FlexSPI_A_D0, FlexSPI_A_D1, FlexSPI_A_D2, FlexSPI_A_D3)

However, due to difficulties in supply of IS25WP128-JBLE (QSPI Flash) used in evk boarad, it was changed to S25FL128LAGMFI010 (QSPI Flash).

The difference between IS25WP128-JBLE and S25FL128LAGMFI010 is about register map configuration or dummy cycle, and is almost similar in use.

We tested by modifying the code based on the example code "flexspi_nor_poling_transfer_cm7" provided by the SDK.

code fixes

"app. h"

CUSTOM_LUT_LENGTH 64U => 128U (*) increase value, uint32_t customLUT[CUSTOM_LUT_LENGTH] add some content for testing purposes

"flexspi_nor_flash_ops.c"

status_t flexspi_nor_enable_quad_mode(FLEXSPI_Type *base) in the function

uint32_t writeValue = FLASH_QUAD_ENABLE; => 0x02; (*) FLASH_QUAD_ENABLE = 0x40U, quad mode enable bit changed according to S25FL128LAGMFI010 change

"flexspi_nor_polling_transfer.c"

uint32_t customLUT[CUSTOM_LUT_LENGTH] in array

[4 * NOR_CMD_LUT_SEQ_IDX_READ_FAST_QUAD + 1] = FLEXSPI_LUT_SEQ(

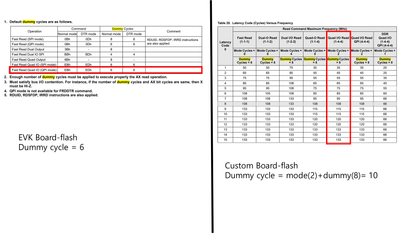

kFLEXSPI_Command_DUMMY_SDR, kFLEXSPI_4PAD, 0x06, kFLEXSPI_Command_READ_SDR, kFLEXSPI_4PAD, 0x04),

=> kFLEXSPI_Command_DUMMY_SDR, kFLEXSPI_4PAD, 0x0A, kFLEXSPI_Command_READ_SDR, kFLEXSPI_4PAD, 0x04),

(*) The function of fast read quad mode is the same as 0xEB, but there is a difference in the dummy cycle 0x06=>0x0A

Only when dummy cycle 8 is applied, all data read is incorrect. When 10 is applied by adding mode cycle (2) to the dummy cycle, some are read as normal, and some are incorrect.

Please check if my code modification is correct, and ask if there may be other causes for the problem.

QE bit is not enabled properly for S25FL128 with your code change. that's why Read and Write of Quad mode do not operate normally.

For IS25WP128, QE bit is in Status Register (1byte sequence), but it is in Configuration register for S25FL128 (2bytes sequence)

Please refer to below project, it supports S25FL064, should be ok for S25FL128 as well

https://github.com/JayHeng/RT-MFB/tree/main/boards/mimxrt/mfb_fw/imxrt1176/cm7

Thank you. Some of the problems were solved by referring to the code you shared. There was an error in the quad mode setup. Quad write was solved by this part modification. There are still problems with quad reads, but this will be fixed soon.