- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MX RT クロスオーバーMCU

- :

- i.MX RT1050 RMII Reference Clock

i.MX RT1050 RMII Reference Clock

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

i.MX RT1050 RMII Reference Clock

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

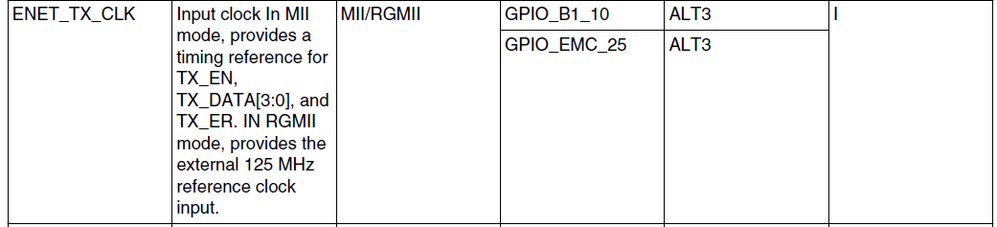

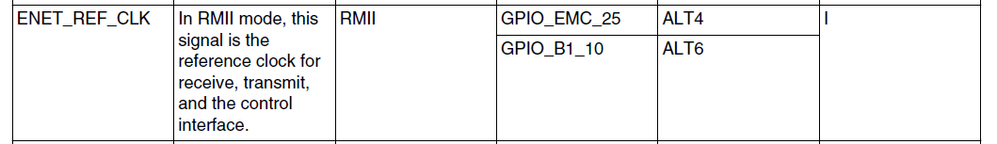

According to the i.MX RT1050 Processor Reference Manual, Rev. 2, the signal ENET_REF_CLK (on pad GPIO_B1_10) is an input in RMII mode. See Table 40-2. ENET External Signals.

Looking at the IMXRT1050-EVKB schematics, however, this signal seems to be an output from the processor, signal name ENET_TX_CLK, which is used to clock the PHY.

Can anybody please explain this apparent difference in documented signal direction.

Thanks for your help,

Pete Baston.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Well, here I know it is really confused. Please be note that both ENET_REF_CLK and ENET_TX_CLK are inputs to the pins you route them to by default. This had been clearly indicated in the Reference manual.

While, it is yes that for IMXRT1050-EVKB, ENET_TX_CLK is used to clock the PHY. This had been done by software.

By configure ENET PLL(Set ENET1_CLK_SEL to 0 to have the ENET1 TX clock driven by the internal ref_enetpll) and set ENET1_TX_CLK_DIR to 1 to enable ENET1_TX_CLK output driver that will redirect the generated clock to the PHY.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Fang,

Thanks for your reply. So, by configuring these bits in software we have the choice of two modes, with the 50MHz reference clock being either an input or an output ?

Why was the 50MHz clock output mode chosen for the EVKB design ? Is this simply to avoid having a crystal on the PHY ?

Best Regards,

Pete.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Yes, your understanding is correct.