- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Re: hard fault set, shows Imprecise data bus error after running for several hours.

hard fault set, shows Imprecise data bus error after running for several hours.

hard fault set, shows Imprecise data bus error after running for several hours.

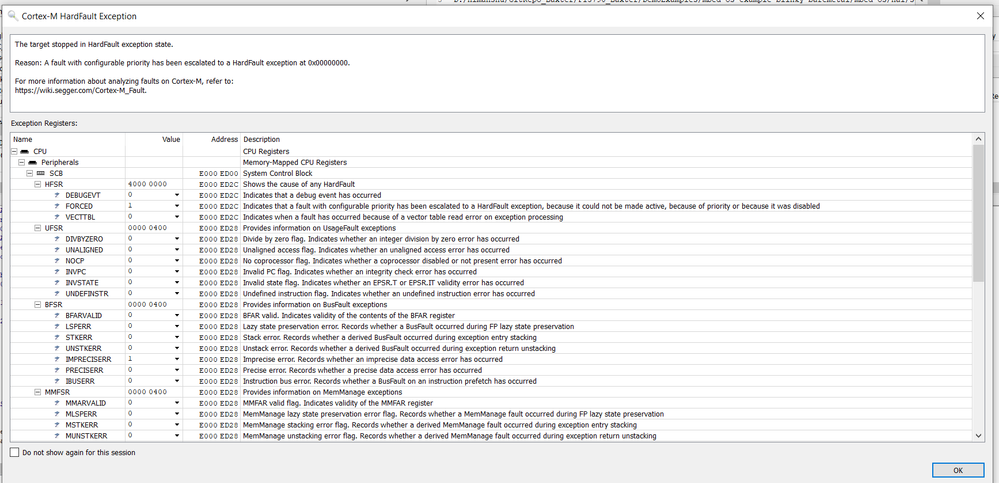

When we are doing a durability test on the CAN send and receive, we had the following hard fault after running the software for several hours:

The Imprecise data bus error bit is set in the BFSR register.

The fault happened randomly after the software has been running for several hours.

We are using NXP MXRT1064

Any clue or suggestion would be appreciated.

Thanks a lot for your help.

Ni

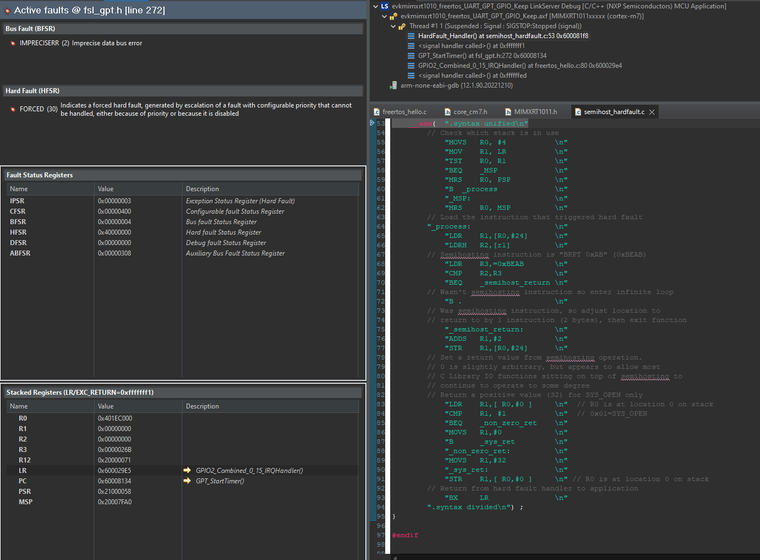

Hello,

I'm having a similar issue, the only difference is that I am starting/stopping a PIT triggered by a rising and falling edge interrupt respectively. Sometimes the code runs fine, sometimes it is slopy and sometimes throws a FAULT.

I tried setting priorities for the 2 interrupts with no effect. I used other pins with no effect. Seems to be a configuration matter, but I can;t put my finger on it. Sampe code below.

BOARD_ConfigMPU();

BOARD_InitBootPins();

BOARD_InitBootClocks();

NVIC_SetPriority(GPIO1_Combined_0_15_IRQn, 0U);//this doesn't solve the issue, although increases consistency

NVIC_SetPriority(GPIO2_Combined_0_15_IRQn, 1U);//this doesn't solve the issue, although increases consistency

BOARD_InitBootPeripherals();