- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- The speed of RT1052 to read data from SDRAM noncache area is very slow

The speed of RT1052 to read data from SDRAM noncache area is very slow

The speed of RT1052 to read data from SDRAM noncache area is very slow

02-07-2023

05:06 AM

384 次查看

I need to read data from SDRAM noncache area.the SDRAM is simulated using FPGA,and it contains ADC result,so it must have noncache attribute.

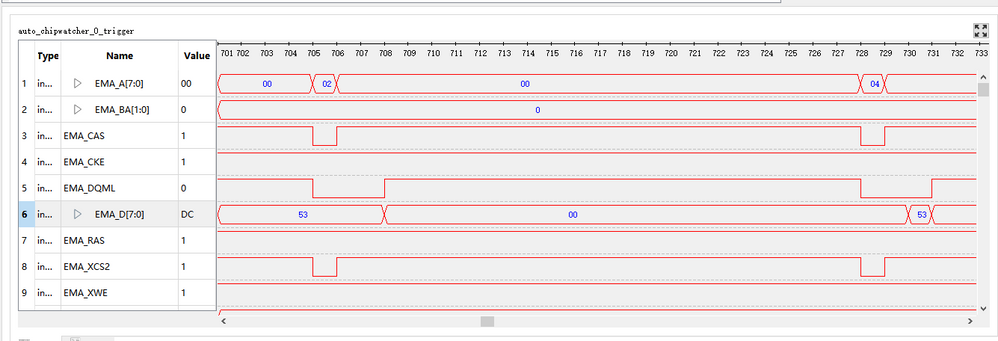

The problem is that it consumes about 1.5us to read 10 uint16_t data.Using FPGA to monitor data transfering on the bus,it shows like the picture below

There are about 26 clocks between two read operation,and during this period,the bus is idle.My CPU works at 528MHz,and SEMC works at 132MHz。

The disassember code that read data from FPGA is listed below:

mov.w r3,0x84000000

add.w r4,r7,#8

mov r5,r3

ldr r0, [r5, #0]

ldr r1, [r5, #4]

ldr r2, [r5, #8]

ldr r3, [r5, #12]

stmia r4!,{r0,r1,r2,r3}

ldr r0,[r5,#16]

str r0,[r4,#0]This code segment locates in the highest priority ISR,There is no possible to be interrupted.

why are there 26 clocks between two read operation?How can i promote reading speed?

Any suggestion is appreciated!

Thanks in advance.

Best regards!

0 回复数