- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MX RT クロスオーバーMCU

- :

- SCK frequency from LPSI4 of mimxrt1170

SCK frequency from LPSI4 of mimxrt1170

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi iam using rt1170 with mcuxpresso sdk my slave device can support up to 40mhz but as of i can able to generate 1mhz only.

which register i want use to change the sclk of rt1170 from 1mhz to 10mhz

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @sandeepc

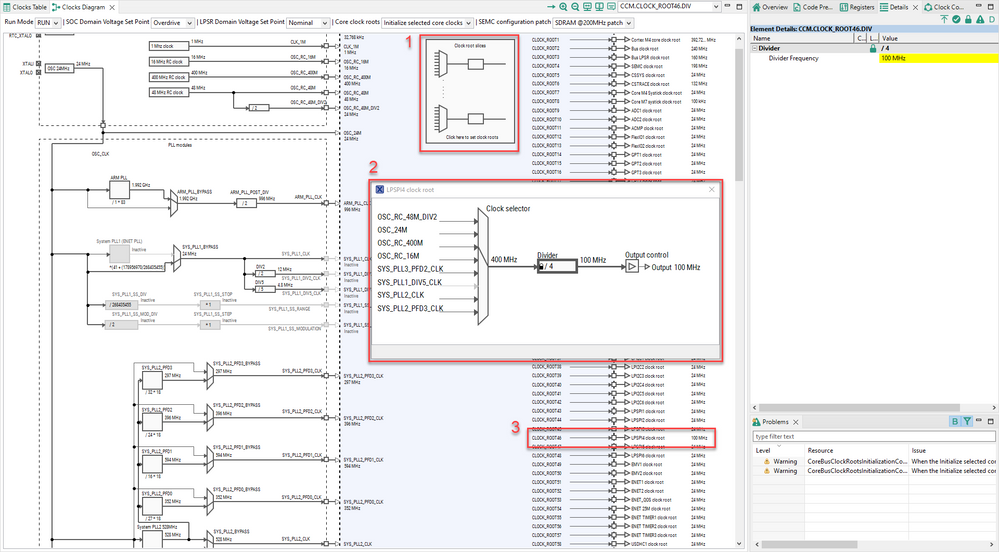

The maximum frequency for the LPSPI4 module is 135MHz. You can increase the source frequency for this module with the clock configuration tool. In this example, I simply double clicked the clock root section, selected LPSPI4 clock root, and changed the source to OSC_RC_400M and divider to /4 in order to increase the default clock frequency from 24MHz all the way to 100MHz. This clock source will allow you to have a higher range for your SCL frequency.

With respect to the community post you reference, it only applies to S32K, not RT.

BR,

Edwin.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @sandeep_c,

Please loot into Section "70.3.1.3 Timing parameters" of the RM for more information about the timing configurations for the SPI modules. There you will find the description of the SCKDIV register, which you will have to adjust in order to change the divider of the modules frequency and that way determine a desired SCL frequency. In other words, the SCL frequency depends on both the SPI source clock as well as it's divider. The function "LPSPI_MasterSetBaudRate()" from the fsl_lpspi.c driver found in our SDK examples shows an optimal way of calculating and asserting a desired baud rate on a chosen LPSPI module, so you can refer to that routine for a proper implementation of baud rate change in your code.

BR,

Edwin.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

LPSPI4_CLK_ROOT 24mhz

#include <stdio.h>

#include "board.h"

#include "peripherals.h"

#include "pin_mux.h"

#include "clock_config.h"

#include "MIMXRT1176_cm7.h"

#include "fsl_debug_console.h"

/* TODO: insert other include files here. */

#include "fsl_lpspi.h"

/* TODO: insert other definitions and declarations here. */

void spi_init(void);

#define LPSPI61 1

#define LPSPI41 0

#if LPSPI41

#define LPSPI_MASTER_CLK_FREQ (CLOCK_GetFreqFromObs(CCM_OBS_LPSPI4_CLK_ROOT))

#endif

#if LPSPI61

#define LPSPI_MASTER_CLK_FREQ (CLOCK_GetFreqFromObs(CCM_OBS_LPSPI6_CLK_ROOT))

#endif

/*

* @brief Application entry point.

*/

//LPSPI_MasterSetBaudRate()

int main(void)

{

unsigned char str[]="hello";

/* Init board hardware. */

BOARD_InitBootPins();

BOARD_InitBootClocks();

BOARD_InitBootPeripherals();

#ifndef BOARD_INIT_DEBUG_CONSOLE_PERIPHERAL

/* Init FSL debug console. */

BOARD_InitDebugConsole();

#endif

spi_init();

PRINTF("Hello World\n");

lpspi_transfer_t fifo_read;

fifo_read.dataSize=6;

fifo_read.rxData=0;

fifo_read.txData=str;

#if LPSPI41

fifo_read.configFlags=kLPSPI_MasterPcs1 | kLPSPI_MasterPcsContinuous | kLPSPI_SlaveByteSwap;

#endif

#if LPSPI61

fifo_read.configFlags=kLPSPI_MasterPcs0 | kLPSPI_MasterPcsContinuous | kLPSPI_SlaveByteSwap;

#endif

while(1)

{

#if LPSPI61

LPSPI_MasterTransferBlocking(LPSPI6,&fifo_read);

#endif

#if LPSPI41

LPSPI_MasterTransferBlocking(LPSPI4,&fifo_read);

#endif

for(int i=1000000;i--;);

}

return 0 ;

}

void spi_init(void)

{

PRINTF("\r\nSPI INTERFACE CALLED");

uint32_t srcClock_Hz;

lpspi_master_config_t masterConfig;

masterConfig.baudRate =10000000;

masterConfig.bitsPerFrame=8;

masterConfig.cpol=kLPSPI_ClockPolarityActiveHigh;

masterConfig.cpha = kLPSPI_ClockPhaseFirstEdge;

masterConfig.direction = kLPSPI_MsbFirst;

masterConfig.pcsToSckDelayInNanoSec=1000;

masterConfig.lastSckToPcsDelayInNanoSec=1000;

masterConfig.betweenTransferDelayInNanoSec=1000;

#if LPSPI41

masterConfig.whichPcs = kLPSPI_Pcs1;

#endif

#if LPSPI61

masterConfig.whichPcs = kLPSPI_Pcs0;

#endif

masterConfig.pinCfg = kLPSPI_SdiInSdoOut;

masterConfig.dataOutConfig=kLpspiDataOutRetained;

masterConfig.pcsActiveHighOrLow=kLPSPI_SdiInSdoOut;

srcClock_Hz = LPSPI_MASTER_CLK_FREQ;

PRINTF("\n\rsrcClock_Hz ==%d\n\r",srcClock_Hz);

#if LPSPI41

LPSPI_MasterInit(LPSPI4, &masterConfig, srcClock_Hz);

#endif

#if LPSPI61

LPSPI_MasterInit(LPSPI6, &masterConfig, srcClock_Hz);

#endif

}

1) as you mentioned LPSPI_MasterSetBaudRate() i used this function this fun returns the best prescale value i checked with diffrent baudrate values

2) the presclae value i changed manually from 0 to 8 in fsl_lpspi.c driver

tcrPrescaleValue=2=28khz

tcrPrescaleValue=4=7khz

tcrPrescaleValue=6=3.5khz

tcrPrescaleValue=8=200khz

/* Set baudrate and delay times*/

(void)LPSPI_MasterSetBaudRate(base, masterConfig->baudRate, srcClock_Hz, &tcrPrescaleValue);

/* Set default watermarks */

LPSPI_SetFifoWatermarks(base, (uint32_t)kLpspiDefaultTxWatermark, (uint32_t)kLpspiDefaultRxWatermark);

// tcrPrescaleValue=0;

/* Set Transmit Command Register*/

base->TCR = LPSPI_TCR_CPOL(masterConfig->cpol) | LPSPI_TCR_CPHA(masterConfig->cpha) |

LPSPI_TCR_LSBF(masterConfig->direction) | LPSPI_TCR_FRAMESZ(masterConfig->bitsPerFrame - 1U) |

LPSPI_TCR_PRESCALE(tcrPrescaleValue) | LPSPI_TCR_PCS(masterConfig->whichPcs);

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

If you are looking for higher baud rates, try using a larger clock source for your module in order to increase the frequency cap of the LPSPI. Use another clock root with a higher frequency, instead of the 24 MHz clock root, and then use that as your srcClock parameter to let the previously mentioned routine adjust to the desired baudrate.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

@EdwinHz thank you what is the maximum source frequency of of lpspi module

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for mentioning this case link but Please check the below link

I have doubt like what is the maximum lpspi src clock and what is the maximum sclk clock? What he mentioned it's for sclk freq or src freq?

How can I calculate the desired baudrate?

What is maximum src frequency clock for lpspi ?

What is maximum sclk frequency i can generate?

What is 28mhz mentioned in above link?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @sandeepc

The maximum frequency for the LPSPI4 module is 135MHz. You can increase the source frequency for this module with the clock configuration tool. In this example, I simply double clicked the clock root section, selected LPSPI4 clock root, and changed the source to OSC_RC_400M and divider to /4 in order to increase the default clock frequency from 24MHz all the way to 100MHz. This clock source will allow you to have a higher range for your SCL frequency.

With respect to the community post you reference, it only applies to S32K, not RT.

BR,

Edwin.