- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Re: RT1064 ENET module incorrectly triggers a receive interrupt.

RT1064 ENET module incorrectly triggers a receive interrupt.

Hello !

I have two RT1064 boards(A and B) and communicate via Ethernet and found a incomprehensible problem.

Test results: Board A sends messages to Board B via Ethernet 10 times in total, with a length of 60 bytes and a transmission interval of 30us. The ENET module of board B can trigger a reception interrupt and receive the correct message. Board A triggers transmission interrupt after calling ENET_Sendframe to send the messages

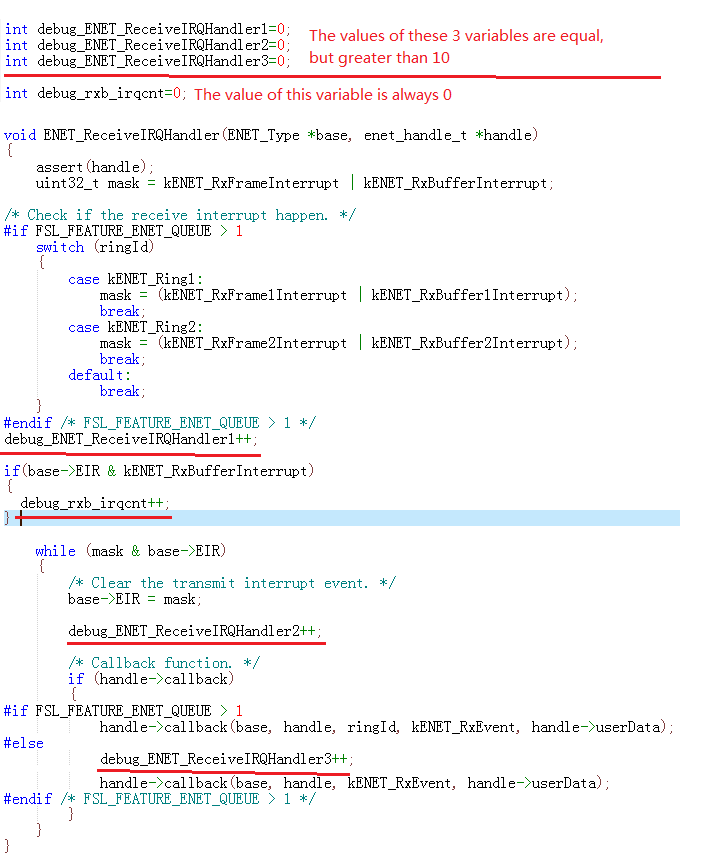

I added a variable to the interrupt processing function of fslenet.c to count the number of interrupts.The number of transmission interrupt counts of board A is 10. But sometimes Board B will repeatedly enter the interrupt by mistake, which is shown as the number of B board reception interrupt is more than 10

Has anyone encountered this kind of problem?Can you give me some suggestions?

Thank you!

已解决! 转到解答。

Hi zeyong yang,

Thanks for your updated information.

Maybe this cache application note will be useful to you:

https://www.nxp.com/docs/en/application-note/AN12042.pdf

4.2. Cache maintenance in SDK Driver

The following drivers in the SDK maintain the data coherency of the cache:

1. Ethernet

In the ENET, a unified DMA (uDMA) engine is designed, it optimizes data transfer between the ENET core and the SoC, and supports an enhanced buffer descriptor programming model to support IEEE 1588 functionality.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi zeyong yang ,

Do you use some PC Ethernet analyze tool to check the board A, whether after your modifications, more data is sent out?

If you still have questions about it, please kindly let me know.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Thanks to kerry.

I used wireshark to monitor the message on the PC, wireshark grabbed 10 messages sent from board A to board B.Only 10 messages,and the message data are correct

FSL_FEATURE_ENET_QUEUE macro does not take effect

In addition, after successfully reading the message data received by ENET, is the receive buffer invalid?

----------------------------------------------------------------------------------------------------------------------

Hi zeyong yang

Just send 1 time, whether the board B will receive more than once?

Any updated information, please kindly let me know.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

I did another test and found a more incredible error:

Board A repeatedly sends 2 different messages: M1 and M2. It is sent in the order of M1-M2-M1. Sometimes the message received by board B is M1-M2-M2

I used wireshark to capture packets, and can see that board A did send M1-M2-M1 in sequence.

I confirmed that board B entered 3 receive interrupts by the variable count

Why did the ENET module lose the M1 message and received the M2 message by mistake

Hi zeyong yang,

Do you use the NXP MIMXRT1064 boards? And do you use the Official SDK code?

If yes, please tell me the reproduce detail steps, then I will try to use the official board to reproduce it, and check more details.

Waiting for your updated information.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Thank to Kerry. I have solved this problem Probably

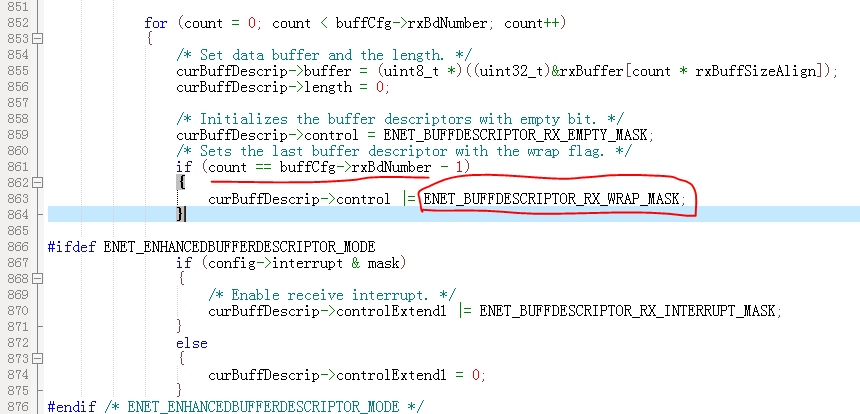

Through a lot of packet analysis, I found the time when the error occurs is that the number of received packets exceeds the value of BD(ENET_RXBD_NUM defined in enet_ethernetif_kinetis.c)

I checked the RT1064 manual and read the code of fslenet.c, FSL_SDK_ENABLE_DRIVER_CACHE_CONTROL macro play a role in many codes

I enable the FSL_SDK_ENABLE_DRIVER_CACHE_CONTROL macro, and the packet reception error is now gone.

FSL_SDK_ENABLE_DRIVER_CACHE_CONTROL macro determines whether to execute DCACHE_InvalidateByRange in ENET_ReadFrame and ENET_SetRxBufferDescriptors

What is the mechanism of this macro? BD is logically a circular buffer, and there is also a judgment in the code whether it reaches the maximum value

Are there other problems with this solution?The macro is not turned on by default for receiving message normally.

Hi zeyong yang,

Thanks for your updated information.

Maybe this cache application note will be useful to you:

https://www.nxp.com/docs/en/application-note/AN12042.pdf

4.2. Cache maintenance in SDK Driver

The following drivers in the SDK maintain the data coherency of the cache:

1. Ethernet

In the ENET, a unified DMA (uDMA) engine is designed, it optimizes data transfer between the ENET core and the SoC, and supports an enhanced buffer descriptor programming model to support IEEE 1588 functionality.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------