- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- Re: RT1052 SEMC - SDRAM Sleep / Low Power

RT1052 SEMC - SDRAM Sleep / Low Power

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How do you put the RT1052's SEMC for SDRAM into low power mode (assuming the same ISSI SDRAM that's used in the EVK, etc)?

I saw some mention of a deep sleep mode for other NXP parts' SEMC.

How do we do the same here?

Might be irrelevant, but we initialize the SDRAM w/ this code:

status_t BOARD_InitSEMC(void)

{

semc_config_t config;

semc_sdram_config_t sdramconfig;

uint32_t clockFrq = CLOCK_GetFreq(kCLOCK_SemcClk);

/* Initializes the MAC configure structure to zero. */

memset(&config, 0, sizeof(semc_config_t));

memset(&sdramconfig, 0, sizeof(semc_sdram_config_t));

/* Initialize SEMC. */

SEMC_GetDefaultConfig(&config);

config.dqsMode = kSEMC_Loopbackdqspad; /* For more accurate timing. */

SEMC_Init(SEMC, &config);

/* Configure SDRAM. */

sdramconfig.csxPinMux = kSEMC_MUXCSX0;

sdramconfig.address = 0x80000000;

sdramconfig.memsize_kbytes = 32 * 1024; /* 32MB = 32*1024*1KBytes*/

sdramconfig.portSize = kSEMC_PortSize16Bit;

sdramconfig.burstLen = kSEMC_Sdram_BurstLen8;

sdramconfig.columnAddrBitNum = kSEMC_SdramColunm_9bit;

sdramconfig.casLatency = kSEMC_LatencyThree;

sdramconfig.tPrecharge2Act_Ns = 18; /* Trp 18ns */

sdramconfig.tAct2ReadWrite_Ns = 18; /* Trcd 18ns */

sdramconfig.tRefreshRecovery_Ns = 67; /* Use the maximum of the (Trfc , Txsr). */

sdramconfig.tWriteRecovery_Ns = 12; /* 12ns */

sdramconfig.tCkeOff_Ns =

42; /* The minimum cycle of SDRAM CLK off state. CKE is off in self refresh at a minimum period tRAS.*/

sdramconfig.tAct2Prechage_Ns = 42; /* Tras 42ns */

sdramconfig.tSelfRefRecovery_Ns = 67;

sdramconfig.tRefresh2Refresh_Ns = 60;

sdramconfig.tAct2Act_Ns = 60;

sdramconfig.tPrescalePeriod_Ns = 160 * (1000000000 / clockFrq);

sdramconfig.refreshPeriod_nsPerRow = 64 * 1000000 / 8192; /* 64ms/8192 */

sdramconfig.refreshUrgThreshold = sdramconfig.refreshPeriod_nsPerRow;

sdramconfig.refreshBurstLen = 1;

return SEMC_ConfigureSDRAM(SEMC, kSEMC_SDRAM_CS0, &sdramconfig, clockFrq);

}Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Andrew,

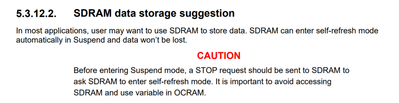

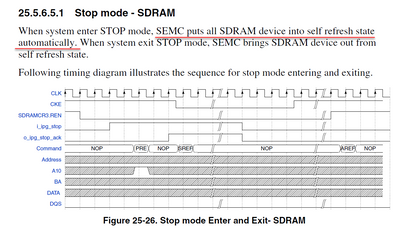

The AN12085 has mentioned below info about SDRAM during RT1052 in low power mode:

And RT1050 reference manual with below info:

The SEMC module will let external SDRAM enter into self refresh mode automatically before chip enter into low power mode.

If you still have concerns, you can use IP command to send SDRAM AUTO REFRESH command with SEMC IP Command register (IPCMD).

Wish it helps.

Mike

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

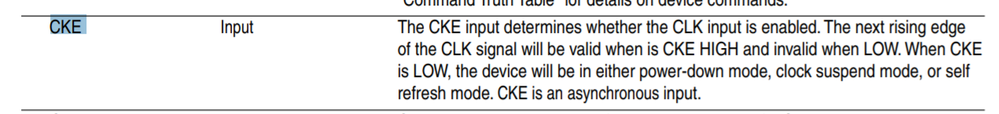

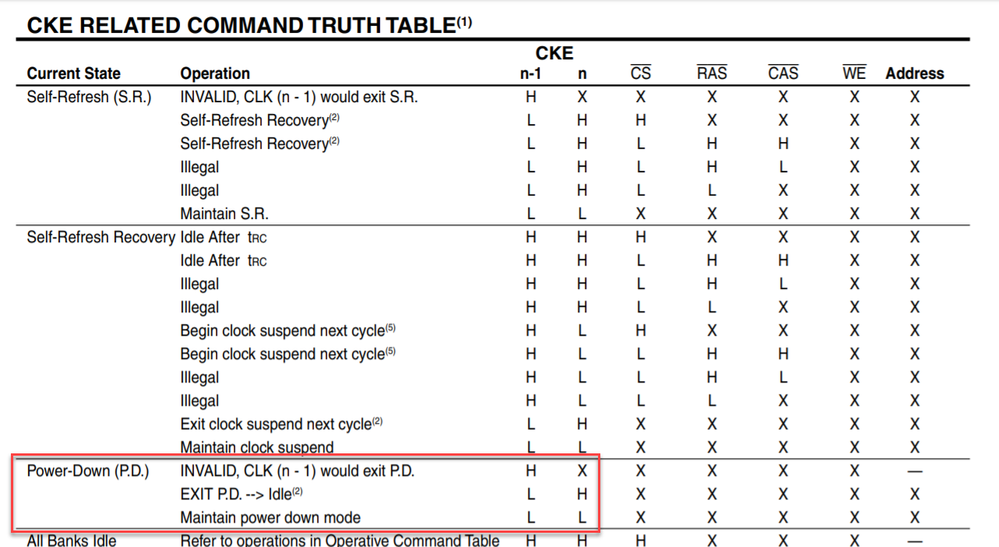

MIMXRT1050-EVKB board using ISSI S42S16160J-6BLI SDRAM with below description to enter into power down mode:

Before customer let external SDRAM enter into power down mode, it need to send SDRAM auto refresh command to external SDRAM.

Wish it helps.

Have a great day,

Mike

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Hui_Ma ,

Sorry for the delayed response - just getting back to power optimization in my project again and looking at SDRAM:

It's not clear to me how to properly do this using the MCUXpresso RT1052 SDK as there is no direct function in the SDK (or in the RT1052 RM) about turning CKE to off via the SEMC.

Do I need to disable the SEMC-SDRAM first via:

SEMC_Deinit(SEMC);

And then change the SEMC's CKE pin (GPIO_EMC_27) to 0 using GPIO, eg:

#define SDRAM_GPIO GPIO4

#define SDRAM_GPIO_CKE_PIN (27U)

gpio_pin_config_t pin_config = {kGPIO_DigitalOutput, 0, kGPIO_NoIntmode};

GPIO_PinInit(SDRAM_GPIO, SDRAM_GPIO_CKE_PIN, &pin_config);

GPIO_PinWrite(SDRAM_GPIO, SDRAM_GPIO_CKE_PIN, 0U);

Or should I be manually forcing CKE down FIRST, and THEN deInit SEMC? or...??

Has someone at NXP/FSL written an example that proves out powering down SDRAM from the i.MX RT parts?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Andrew,

The AN12085 has mentioned below info about SDRAM during RT1052 in low power mode:

And RT1050 reference manual with below info:

The SEMC module will let external SDRAM enter into self refresh mode automatically before chip enter into low power mode.

If you still have concerns, you can use IP command to send SDRAM AUTO REFRESH command with SEMC IP Command register (IPCMD).

Wish it helps.

Mike