- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MX RT クロスオーバーMCU

- :

- Re: PWM using Flexio_PWM

PWM using Flexio_PWM

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

PWM using Flexio_PWM

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

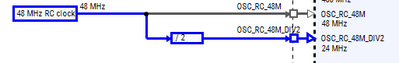

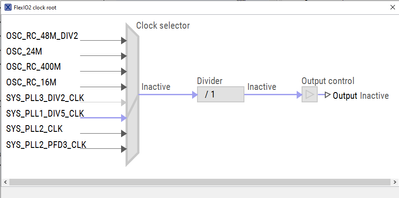

I am trying to generate a PWM signal with Frequency=20Hz and DC=14%.I imported the flexio_pwm example from SDK which uses generates PWM at frequency=47MHz using kCLOCK_Root_Flexio2, i.e. 24Mhz.

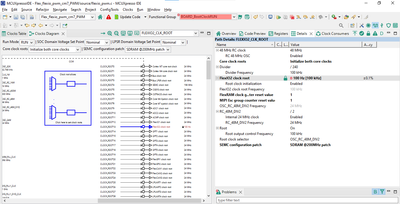

But my application requires very low frequency <100Hz, when I try to change in Clock Configuration tool, it is showing error:

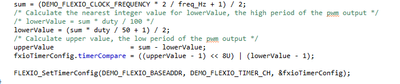

and also I tried setting to 100kHz, now clock configuration updated fine but in my source code,

there is a calculation of sum, lower & upper values which set the timer compare. when I'm using 100kHz as clock frequency, I'm getting value more than uint32_t.

Is there any other provision to use clock configuration or other method to figure out the issue.

Thanks & regards,

Manikanta Robbi.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thank you so much for your interest in our products and for using our community.

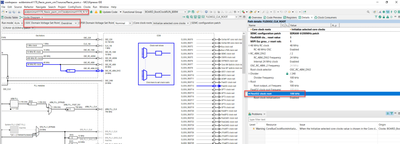

You need to change the SOC domain voltage set point.

Hope it helps you.

Have a nice day!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks @_Leo_ ,

For the information, I had tried changing SOC Domain Voltage Set Point, but not able to set 100KHz for FlexIO2 Clock root. Can you please guide steps to change and provide Application note or Reference manual.

Thanks & Regards,

Manikanta Robbi.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

As per guidance, I changed SOC Domain voltage point: Normal. And changed so configurations like

1)creating new functional group.

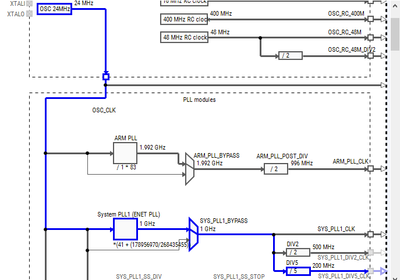

2)Enabling SYS_PLL_DIV5_CLK.

But the problem arises, when flashing code to MCU (resetting) or Not able to enter into Debug mode, Why? Is there any effect changing clock from 48Mhz to any PLL (ARM, or any similar options mention in the clock tree) may impact code flashing into memory.

Thanks & Regards,

Manikanta Robbi.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @_Leo_ ,

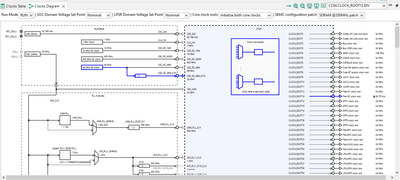

I had found that clock is changing fine when we select: 48MHZ RC OSC

But the issue, when I configure with:SYS_PLL1_DIV5(making as active)

Note: this SYS_PLL is chosen from: External 24MHz Crystal

Why I'm not able to get frequency configured using PLL (by opting OSC_24MHz).

Thanks,

Manikanta Robbi.