- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- On an RT106x, how do you use SEMC_MCR.DQSMD = 0 (to free up EMC_39 for a spare GPIO)?

On an RT106x, how do you use SEMC_MCR.DQSMD = 0 (to free up EMC_39 for a spare GPIO)?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

An RT106x board with SDRAM I've been asked to look at has been designed to use EMC_39 as a spare GPIO. Reading the Reference Manual, it seems the way to configure the registers for this would be to set DQSMD = 0 (in the SEMC_MCR register) and then set up the ALT5 pinmux for EMC_39.

However, even though the SDRAM currently works fine with DQSMD = 1, the moment I set DQSMD to 0 the SDRAM stops working (and this is in EMC_39's ALT0 pinmux mode, never mind the ALT5 mode).

My best guess is that the SEMC timings for the SDRAM would need to be edited in order to get DQSMD = 0 working, but I think I'm missing some key information to achieve this.

What would I need to do to get DQSMD = 0 this working? Is DQSMD = 0 (disabled) much slower than DQSMD = 1 (enabled)?

All hints and suggestions gratefully received!

Thanks, Nick

PS: the two closest posts I found were this RT1050 one from 2019 by David Rodgers ( @dmarks_ls

https://community.nxp.com/t5/i-MX-RT/RT1050-Can-SDRAM-DQS-be-looped-back-internally/m-p/907390

...and this RT1020 post from 2020 by Ronnie Shipman ( @rshipman

https://community.nxp.com/t5/i-MX-RT/RT1020-clocking-SDRAM-at-166Mhz-Zero-timing-margin/m-p/1039370

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

In order to move from DQSMD 1 to DQSMD 0 you must (first) reduce the SEMC_CLK_ROOT speed to about 60MHz.

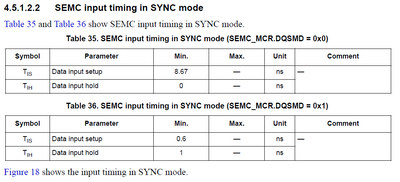

From the data sheet it is seen that 133/166MHz speed is not supported when using the alternative configuration:

See pages 20..21 of https://www.utasker.com/docs/iMX/i.MX_RT_1021_uTasker.pdf for SEMC clock settings and check how it is set as default (eg. via DCD) then increase the root divide value (SEMC_PODF) in CCM_CBCDR accordingly.

This can either be done generally in the DCD or else the DCD can be set for full speed and then the change be made on-the-fly when the GPIO is needed - note however that the pin should usually be left floating for the highest speed of operation ad not connected to external circuitry.

Regards

Mark

[uTasker project developer for Kinetis and i.MX RT]

Contact me by personal message or on the uTasker web site to discuss professional training, solutions to problems or rapid product development requirements

For professionals searching for faster, problem-free Kinetis and i.MX RT 10xx developments the uTasker project holds the key: https://www.utasker.com/iMX/RT1060.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Note #1: I know that the DQSMD setting is editable via the SEMC configuration structure in the SEMC peripheral, i.e. Dummy read strobe mode = "Dummy read strobe loopbacked internally". But I don't know how to recalculate the SDRAM configuration settings to make it actually work.

Note #2: it seems @mjbcswitzerland may have attempted something along these lines, as per:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

In order to move from DQSMD 1 to DQSMD 0 you must (first) reduce the SEMC_CLK_ROOT speed to about 60MHz.

From the data sheet it is seen that 133/166MHz speed is not supported when using the alternative configuration:

See pages 20..21 of https://www.utasker.com/docs/iMX/i.MX_RT_1021_uTasker.pdf for SEMC clock settings and check how it is set as default (eg. via DCD) then increase the root divide value (SEMC_PODF) in CCM_CBCDR accordingly.

This can either be done generally in the DCD or else the DCD can be set for full speed and then the change be made on-the-fly when the GPIO is needed - note however that the pin should usually be left floating for the highest speed of operation ad not connected to external circuitry.

Regards

Mark

[uTasker project developer for Kinetis and i.MX RT]

Contact me by personal message or on the uTasker web site to discuss professional training, solutions to problems or rapid product development requirements

For professionals searching for faster, problem-free Kinetis and i.MX RT 10xx developments the uTasker project holds the key: https://www.utasker.com/iMX/RT1060.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content