- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Re: Not able to debug after FlexRAM modification

Not able to debug after FlexRAM modification

Not able to debug after FlexRAM modification

Hi,

We have referred Dec 3, 2019 10:50 PM thread for Flexram modification but not able to debug with PE micro.

We have verified our application run without debugging by following modification suggested in Feb 24, 2020 7:15 AM

As per Dec 3, 2019 10:50 PM, Changes required in connect script. Linkserver script already shared but could not found for PE Micro.

Could you please help with connect script for PE Micro.

Hi jtro 9,

Please also note, if you enable the MPU, you also need to modify the MPU RAM configution.

void BOARD_ConfigMPU(void)

/* Region 4 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(4, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_64KB);

/* Region 5 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(5, 0x20000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_128KB);

/* Region 6 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(6, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_64KB);

Wish it helps you.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi jtro 9,

Today, I also checked the details about the MIMXRT flexRAM configuration script for MCUXPresso IDE, I also didn't find the related item or the related script now.

But, I already help you to check it with the P&E Micro side, whether they have the related information.

In the meanwhile, I suggest you to use the CMSIS DAP debugger for this function at first. Because I am not sure PE micro side have it or not.

Any valuable feedback from p&e micro side, I will let you know.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi jtro 9,

Normally, this also needs the debugger product company's help.

I have contacted with our MCUXPresso IDE department team in the previous time, they told me, they mainly support the CMSIS DAP script, for the other 3rd part debugger, it need the debugger company's support.

Anyway, if I get any valuable reply from P&E micro side, I will let you know.

If you really have time limit, I suggest you use the LPC-LINK2 firmware with CMSIS DAP debugger to debug your RT chip at first.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi,

I have tested GPIO demo code with RT1020-EVK board and found that it is not working as explained in post #1.

Example code I have attached, you can find script file inside project folder.

I have modified script as below

360 REM ====== Configure FlexRAM ======

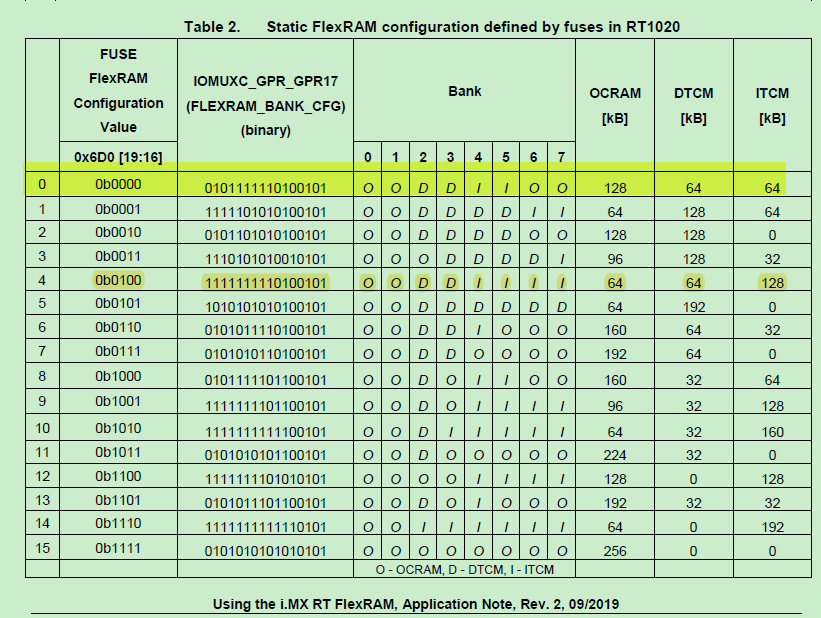

370 print "Configure FlexRAM for 64KB OC RAM, 64KB I-TCM, 128KB D-TCM"

380 REM TCM CTRL Poke 0x400B0000 - to force RAM clocking and set wait states = b100

390 Poke32 this 0x400B0000 0x4

400 REM IOMUXC_GPR17 0x400AC044 - this sets bitfield allocation of FlexRAM 32KB banks to OC 128KB b01, I 64KB b11, D 64KB b10

410 Poke32 this 0x400AC044 0xFAA5

420 REM IOMUXC_GPR16 0x400AC040 - this sets enables for I and DTCM and the source of the TCM config = 0x200007

430 Poke32 this 0x400AC040 0x200007

440 print "Finished"

450 REM ===============================

Hi jtro 9,

RT1020 chip FlexRAM in default is OCRAM 128K, ITCM 64k, DTCM 64k.

Please tell me your new divided situation:

Then I will help you to test it.

Please tell me the above item, which one is your want configuration?

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi jtro 9,

So sorry for my later reply!

Today, I have found the time to test the MIMXRT1020 FlexRAM, your situation, totally the same as MIMXRT1050 operation.

Let's take the MIMXRT1020 SDK led_blinky as an example.

DTCM - 128KB ; ITCM - 64 KB; OCRAM - 64KB

Please note these points:

1. Modify the FlexRAM memory:

2. prepare the CMSIS DAP script

The content is :

100 REM ===============================

110 REM RT1020_connect.scp

120 REM

130 REM Copyright 2019 NXP

140 REM All rights reserved.

150 REM ===============================

160 print "RT10s0 Connect Script"

170 REM probelist

180 p% = probefirstfound

190 rem probeopenbyindex p%

200 wireswdconnect p%

210 selectprobecore p% 0

220 cminitapdp this

230 cmhalt this

235 goto 320

240 rem trap in bootrom

250 cmwatchset this 0 0x400F8004 RW

260 cmresetvectorcatchclear this

270 print "Resetting and trapping"

280 cmsysresetreq this

290 print "Back from reset"

300 cmresetvectorcatchset this

310 cmwatchclear this 0

320 print "Disabling MPU"

330 s% = Peek32 this 0xE000ED94

340 s% = s% & 0xFFFFFFFE

350 Poke32 this 0xE000ED94 s%

360 REM ====== Configure FlexRAM ======

370 print "Configure FlexRAM for 64KB OC RAM, 64KB I-TCM, 128KB D-TCM"

380 REM TCM CTRL Poke 0x400B0000 - to force RAM clocking and set wait states = b100

390 Poke32 this 0x400B0000 0x4

400 REM IOMUXC_GPR17 0x400AC044 - this sets bitfield allocation of FlexRAM 32KB banks to OC 64KB b01, I 64KB b11, D 128KB b10

410 Poke32 this 0x400AC044 0x0000FAA5

420 REM IOMUXC_GPR16 0x400AC040 - this sets enables for I and DTCM and the source of the TCM config = 0x200007

430 Poke32 this 0x400AC040 0x200007

440 print "Finished"

450 REM ===============================

460 end

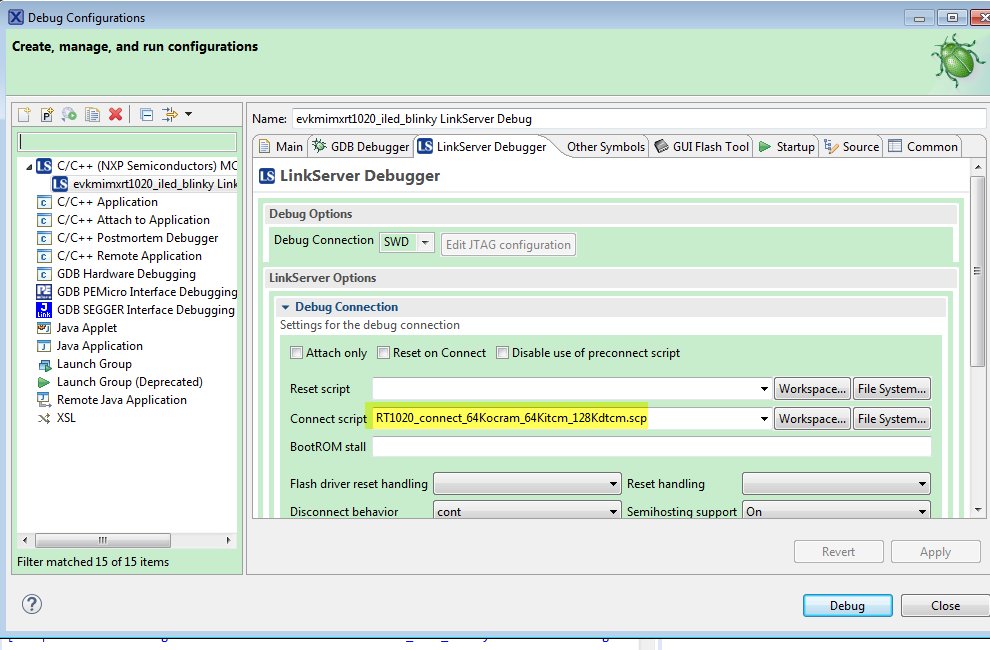

Copy the script(RT1020_connect_64Kocram_64Kitcm_128Kdtcm.scp) to MCUXPresso IDE install path:

C:\nxp\MCUXpressoIDE_11.1.0_3209\ide\binaries\Scripts

3. Select the scp in the MCUXPresso IDE debug configuration

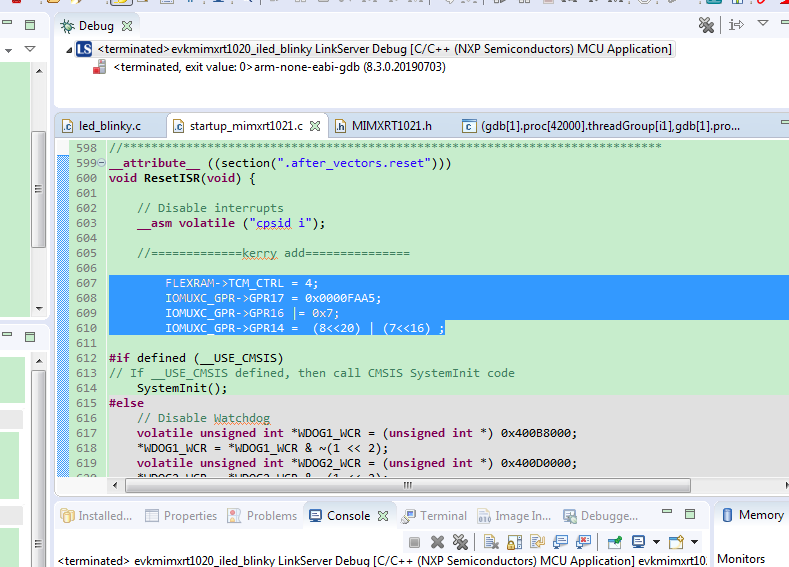

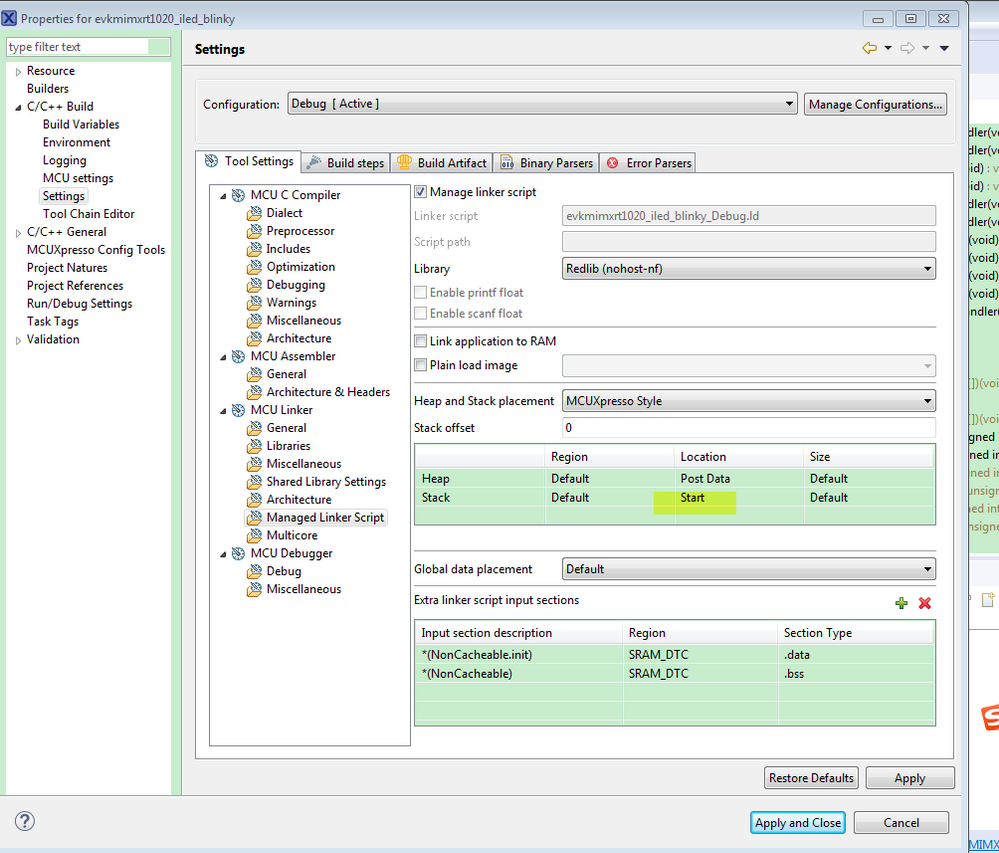

4. Add code in the ResetISR

FLEXRAM->TCM_CTRL = 4;

IOMUXC_GPR->GPR17 = 0x0000FAA5;

IOMUXC_GPR->GPR16 |= 0x7;

IOMUXC_GPR->GPR14 = (8<<20) | (7<<16) ;5. Modify the stack location as start

Then build the project, and download it to your MIMXRT1020-EVK board, no matter debug or exit debug and repower on it, the led will blink.

I also attach my project for your reference.

Wish it helps you.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi jtro 9 ,

Thanks a lot for your cooperation.

What's the board you are using? Also MIMXRT1050-EVKB, then you just used the external P&E Multilink?

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi jtro 9,

OK, let's use the same platform, MIMXRT1020-EVK board.

Do you try the MIMXRT1020-EVK board with CMSIS DAP on board debugger, then follow the RT1050's recommend steps, whether your FlexRAM modification works or not?

Or just the P&E Multilink can't work?

In fact, about the P&E Multilink script, we still need the P&E Micro side help.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

No, we have not tried with on board debugger because we have our own custom board for development. At present we have only one board and three person working on same project so not possible to take debug connection from EVK and work.

Would be much helpful if you provide PE micro script.

Hi jtro 9,

OK,I will use MIMXRT1020-EVK test it, please give me more time, and keep patient, thanks!

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------