- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Re: MIMXRT685-EVK_How to "Write" data when I3C command transfer direction is set as "

MIMXRT685-EVK_How to "Write" data when I3C command transfer direction is set as "Read"?

MIMXRT685-EVK_How to "Write" data when I3C command transfer direction is set as "Read"?

Hi @kerryzhou ,

Let me introduce the test we are trying to do again:

Our client have an original I3C master and the I3C slave made by them.

And they wish to replace the original I3C master with RT685.

The testing we are using to evaluate the replacement is to read the ID data of I3C slave.

After we using scope to capture the behavior of original I3C master to read ID data, we can get three command line and decode as below:

Command1. [Start+0x7E+Write+Ack, Sr+0x18+Write+Ack, 0xXX, 0xXX, 0x01, ... confidential data]

Command2. [Start+0x7E+Write+Ack, Sr+0x18+Read+Ack, 0xXX, 0xXX, 0x02, ... confidential data]

Command3. [Start+0x7E+Write+Ack, Sr+0x18+Read+Ack, 4 byte ID data]

In above command, the 5th byte of command1 and 2 are represent the type of message.

Also, the Command2 and Command3 are the Read command structure.

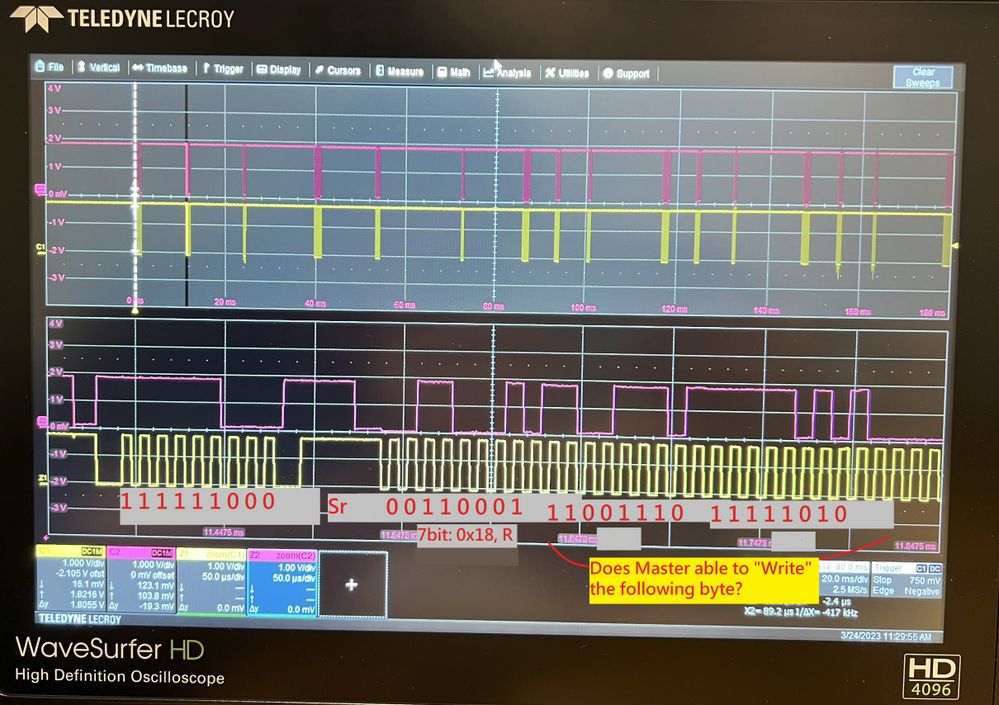

And below is the waveform of command2 from original I3C Master:

According to your previous suggestion of Private RnW transfer, we need to separate the 0x7E and 0x18, and let 0x18 as slave address for next TransferBlocking.

However, according to the waveform, that Master is still transfer data to Slave in command2.

(Because you can see the 8th bit of 0x18 is High, which represent "Read".)

But if the direction is set as "Read", then Master are not able to send following data.

So, our new question is, does the RT685 able to re-build the customized I3C Read structure of Command2 and Command3?

If it's possible, could we have a short meeting to discuss about this issue?

Have a nice day,

Jin Tien

Hi,

Can I propose we start with MIPI standard private read as an example, to see whether the standard read also have issue?

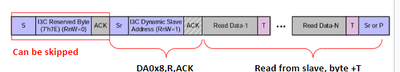

Start->0x7e->ack->Sr->Slave_DA->R->ACK->ReadData1->T->ReadData2->....ReadDataN->T->Stop

where Start->0x7e->ack can be skipped. Sr->Slave_DA->R, Stop from controller; ACK, ReadData, T from target

Hi @ChenpengHuang ,

The SDK I3C default code is the standard read without the 7E, that works OK.

masterXfer.slaveAddress = slaveAddr;

masterXfer.data = g_master_rxBuff;

masterXfer.dataSize = I3C_DATA_LENGTH - 1U;

masterXfer.direction = kI3C_Read;

masterXfer.busType = kI3C_TypeI3CSdr;

masterXfer.flags = kI3C_TransferDefaultFlag;

masterXfer.ibiResponse = kI3C_IbiRespAckMandatory;

result = I3C_MasterTransferBlocking(EXAMPLE_MASTER, &masterXfer);

Now, the private issue is, after sending out the 7E for read, the restart can't be out.

Best Regards,

Kerry.

Hi Kerry,

I switched to the I3C_polling_master sdk library but it seems this one doesn't give me the proper I3C bit stream nor the timing. While when I use the i3c_bus sdk library, RESET DA and SETDASA is working fine, timing and bit stream is perfectly aligned with MIPI I3C spec. I attach both code and waveform I captured for reference, please suggest how should I fix the i3c_polling master_library to get more progress.

I'm in the US time zone, I feel like a real time debug meeting maybe more efficient, please let me know if any FAE is in PST time zone that we can schedule it out.

Hi @ChenpengHuang ,

Sorry for my later reply because of the NXP web login issues.

1. I3C_polling_master

This is first phase also contains the I2C code, you may need to remove the I2C code, then call the I3C code, then that works with I3C.

2. FAE sitaution

In fact, in your case attached email previously, you already have the related FAE, you can contact him.

Best Regards,

Kerry

With it

Hi Kerry,

I’m playing with the library used in i3c_bus demo which mentioned by Frank, called i3c_component.h not the i3c polling master demo under SDK driver. Is there a private read demo using that library?

Hi @Jin_Tien ,

The Private read really have issues, we also meet issues, and the internal RD team also checking it.

Seems the private read with 7E is not supported.

Any updated information, will let you know.

Best Regards,

kerry

Hi @Jin_Tien ,

Thanks so much for your information.

Please keep patient, these days, really a lot of cases in the queue, we are a little overflow.

I will find time to help you do the testing, and give you the response.

BTW, do you also reproduce the issues when both master and slave is the RT685-EVK board?

Best Regards,

Kerry

Hi @kerryzhou ,

Thanks for your reply.

We only have one MIMXRT685-EVK board, sorry that we can't reproduce with two EVK boards.

If you need a meeting to help you know better, please feel free to ask me, thanks a lot.

Have a nice day,

Jin Tien

So sorry for my later reply, really a little overflow, as a lot of testing cases.

Tomorrow, I will help you test it, and give you the updated information, please keep patient, thanks.

Best Regards,

Kerry

Hi @Jin_Tien ,

I am checking your situation, but need your confirmation, this is your question:

"

However, according to the waveform, that Master is still transfer data to Slave in command2.

(Because you can see the 8th bit of 0x18 is High, which represent "Read".)

But if the direction is set as "Read", then Master are not able to send following data.

So, our new question is, does the RT685 able to re-build the customized I3C Read structure of Command2 and Command3?

"

1. Master is still transfer data to Slave in command2.

I want to know: How do you know the master is still transfer data to slave in command2, whether the data is from the slave or not? As normally, in the read mode, the master just sendout the clock, the data is from the slave, so I am a little confusing, whether your data is from slave side, can you confirm it is not from your slave side?

2. But if the direction is set as "Read", then Master are not able to send following data.

I am also confusing, 1 is read, in item 1, you mention it is read, it has data following, but why here you mention master not able to send data? In fact, master should send the clocks not the data.

3. the RT685 able to re-build the customized I3C Read structure of Command2 and Command3?

I think it's OK.

Please help me to confirm it, as I also need to write the related slave code, as I don't have your slave modules.

Best Regards,

Kerry

Hi @kerryzhou ,

Update my feedback as below:

1. Master is still transfer data to Slave in command2.

I want to know: How do you know the master is still transfer data to slave in command2, whether the data is from the slave or not? As normally, in the read mode, the master just sendout the clock, the data is from the slave, so I am a little confusing, whether your data is from slave side, can you confirm it is not from your slave side?

>> The reason why we think the command2 is still write command as below 2 points:

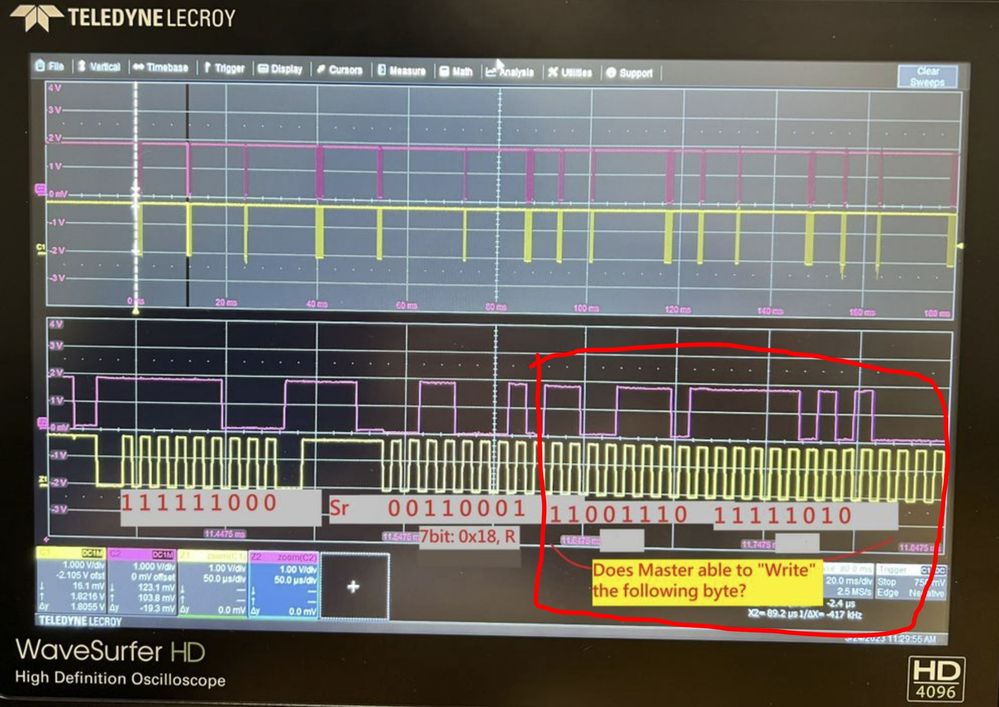

a. In below waveform, the red mark is the customized header defined in client's document.

The slave won't reply the header data as below.

b. As my previous description in below:

And the 5th byte in command2 is 0x02, it has been defined as "Response", which means the Master is asking Slave to response data.

According to above two investigation, we think the Master is still sending data in command2.

Because the document is confidential, sorry that I can not upload the document on community.

2. But if the direction is set as "Read", then Master are not able to send following data.

I am also confusing, 1 is read, in item 1, you mention it is read, it has data following, but why here you mention master not able to send data? In fact, master should send the clocks not the data.

>> As my above reply, the following data you see in the waveform is not sending by Slave.

Because the following data is header defined by client, and it will be sent by Master.

And we know that Master should send clock when RnW = 1, so that's why we say it's a "Customized" structure.

If you still confusing, maybe we can have a personal meeting to help us knowing better, do you think it's possible?

Have a nice day,

Jin Tien

Sharing me your main.c, especially the read command which you think is still sending data, I will try it on my RT685-EVK board. As I don't have your slave, I will use another I3C as the slave, don't know whether it works or not with your situation.

Anyway, I can try it on my side.

Best Regards,

kerry

Hi @kerryzhou ,

Do you mean you want the code of primary master and slave? Because it's py code, and it's provide from our client, so I think it's hard to provide to you.

I only can provide the main.c code I wrote.

Have a nice day,

Jin Tien