- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- MIMXRT 1052 RTWDOG watchdog issue when running on RAM

MIMXRT 1052 RTWDOG watchdog issue when running on RAM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are working on RTWDOG and using SDK SDK_2.5.1_MIMXRT1052xxxxB and IMXRT1050 EVKB board for development.

We are using RTWDOG example from above SDK. RTWDOG reset correctly when refresh is disabled, this module works fine with linker file MIMXRT1052xxxxx_flexspi_nor.icf on IAR. But when we change linker file to MIMXRT1052xxxxx_ram.icf, refresh works fine and when we disabled refresh it goes to some unknow location.

Our requirement is to use one linker file(MIMXRT1052xxxxx_ram.icf) for RTWDOG, UART, I2C and other peripherals. We have tried some changes in liker and RTWDOG example code but still RTWDOG reset is going to some unknown location. Is it possible to use MIMXRT1052xxxxx_ram.icf for RTWDOG? if yes then what changes we have to do in RTWDOG?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @shaileshnsec ,

You are Good!

Now, follow me to generate the .s19 file for the IAR.

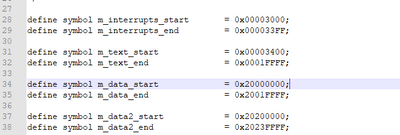

In IAR project, MIMXRT1052xxxxx_ram.icf, modify the interrupt and the text code like this:

define symbol m_interrupts_start = 0x00003000;

define symbol m_interrupts_end = 0x000033FF;

define symbol m_text_start = 0x00003400;

define symbol m_text_end = 0x0001CFFF;

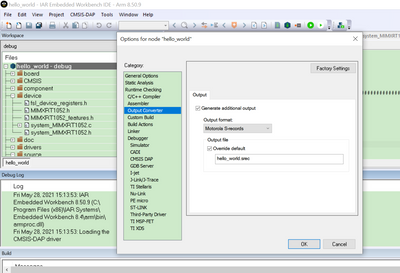

Then, before you build, configure the output file as .srec, it is just the .s19

Ok, use the generated .srec app associated with MCUBootUtility tool to download your own iar .srec, check the function again.

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

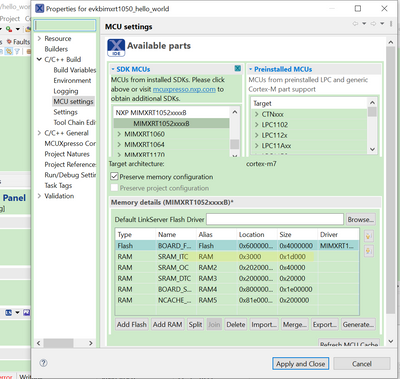

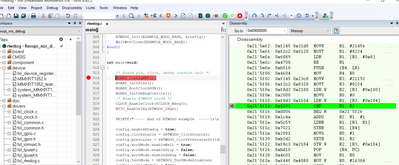

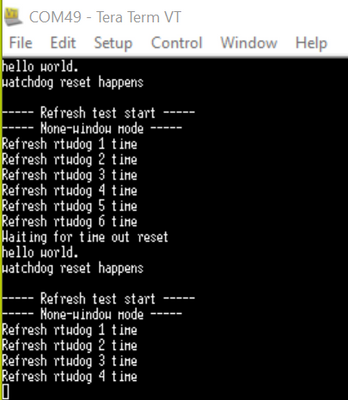

After my testing, I think your issues is mainly the debug with IDE issues, in fact, I generate RAM RTWDOG code, then use the MCUbootUtility tool download to the external flash, and boot and run from RAM, the RTWDOG totally works, I mean, without refresh, the code will be reset, and run it again.

Here I am using the MCUxpresso IDE to generate the RAM code, please note, locate the code from 0X3000, then generate the code, and download it to the flash, I share my test result when I use the MCUbootUtility tool download the generated .s19 files.

I attach my code, evkbimxrt1050_hello_world.s19 can be found in folder: evkbimxrt1050_hello_world\Debug

You can find the reset always happen when I don't update the watchdog.

Wish it helps you!

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your interest in the NXP MIMXRT product, I would like to provide service for you.

Could you please tell me you test the code for your company product?

If yes, it's better to use your company email to create the account and the questions, as more deep discuss need the customer detail information.

You said, you modify the linker, could you please tell me the detail points? And also provide the screen picture which demonstrates you enter the unknown location.

BTW, your SDK is very old, please download the newest SDK2.9.1 for RT1050, do you also test the code on MIMXRT1050-EVKB board?

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank Kerry for response.

Could you please tell me you test the code for your company product? -> Yes but for development we are testing on IMXRT1050-EVKB board and using RTWDOG example code of NXP.

As we have two linker one (MIMXRT1052xxxxx_flexspi_nor.icf) which runs on FlexSPI/ FlexSPI ciphertex location 0x60000000 and other (MIMXRT1052xxxxx_ram.icf) which load code from 0x00000000 location.

1. With linker MIMXRT1052xxxxx_flexspi_nor.icf -> refresh, reset works fine and hits main on every reset when refresh is disabled.

In complier settings of IAR below settings are enabled.

XIP_EXTERNAL_FLASH=1

XIP_BOOT_HEADER_ENABLE=1

2. But with linker MIMXRT1052xxxxx_ram.icf -> refresh works fine but when refresh is disable during reset it goes to unknow location(0x215f14 -> ROMCP) and never hits main.

In complier settings of IAR below settings are enabled.

XIP_EXTERNAL_FLASH=0

XIP_BOOT_HEADER_ENABLE=0

Before integrating to other module we are testing RTWDOG separately. Below code which I am testing on both linker file.

/* Board pin, clock, debug console init */

BOARD_ConfigMPU();

BOARD_InitPins();

BOARD_BootClockRUN();

BOARD_InitDebugConsole();

/* Enable RTWDOG clock */

CLOCK_EnableClock(kCLOCK_Wdog3);

NVIC_EnableIRQ(RTWDOG_IRQn);

PRINTF("----- End of RTWDOG example -----\r\n\r\n");

config.enableRtwdog = true;

config.clockSource = kRTWDOG_ClockSource1;

config.prescaler = kRTWDOG_ClockPrescalerDivide1;

config.workMode.enableWait = true;

config.workMode.enableStop = false;

config.workMode.enableDebug = false;

config.testMode = kRTWDOG_TestModeDisabled;

config.enableUpdate = true;

config.enableInterrupt = false;

config.enableWindowMode = false;

config.windowValue = 0U;

config.timeoutValue = 0xFFFFU;

config.testMode = kRTWDOG_UserModeEnabled;

config.clockSource = kRTWDOG_ClockSource0;

config.prescaler = kRTWDOG_ClockPrescalerDivide256;

config.windowValue = 6000U;

config.timeoutValue = 60000U;

PRINTF("\r\n----- Refresh test start -----\r\n");

/* Refresh test in none-window mode */

PRINTF("----- None-window mode -----\r\n");

config.enableWindowMode = false;

config.enableRtwdog = true;

RTWDOG_Init(EXAMPLE_WDOG_BASE, &config);

while(1)

{

for (int i = 0; i < 10; i++)

{

for (;;)

{

if (1000 * i < RTWDOG_GetCounterValue(EXAMPLE_WDOG_BASE))

{

PRINTF("Refresh value RTWDOG->CNT%d \r\n", RTWDOG->CNT);

//RTWDOG_Refresh(EXAMPLE_WDOG_BASE);

break;

}

}

}

}

We are using same linker file what NXP has given.

Please let me know if need any more information.

Thanks / Shailesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I find it is the debug with IDE debug issues.

Please check my previous new reply, I already generate the RAM firmware, and download to the flash, then boot and run from the RAM again, it totally works.

You also can use your IAR generate the RAM code, and use the MCUBootUtility download it to the flash, and boot again.

Please note, when your use the RAM, the start address, set to 0X3000, or at least 0X2000, then the RAM length- the offset length.

Please try my method, I have tested it, it works OK.

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi kerry,

Could you please share IAR code for RTWDOG which is running on RAM(MIMXRT1052xxxxx_ram.icf)? We are testing on debug mode.

We are not able to generate also we don't have much time.

Thanks / Shailesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

debug method really have issues when run in RAM when the watchdog reset happens. I have tested it.

That's why I suggest you download the RAM code to the flash and run it directly instead of the debug it, when you want to debug, flash method don't have issues.

If you want to run in the RAM, I suggest you download RAM code to the flash and run it.

In fact, I already provide the .s19 to you, you even just need to use the MCUBootUtility download it on your side, as I also have tested it, that works.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks again,

I am little new to MIMXRT1052 processor. As you suggested to download RAM code in flash.

I have set offset in linker file(MIMXRT1052xxxxx_ram.icf) 0x3000 .

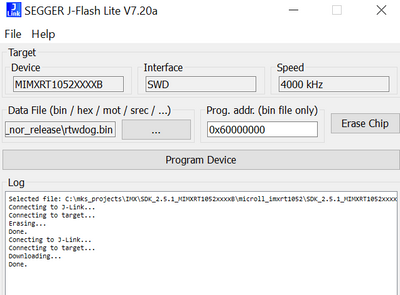

I loaded RTWDOG RAM code with above linker modification in flash location (0x6000 0000) using Segger JFlashLite.exe for run mode. When I power the board it doesn't show any print message on console, seems code is not flashed correctly or may be on wrong location. MCUBootUtility I find more complex if you have doc to show steps to flash, please share.

question is,

1. when we talk about load code in flash mean loading code in this location

??

2. What should be status for SW7 in MIMXRT1050 EVKB board when downloading code to flash ?

3. How does reset sequence happens in RTWDOG RAM in run mode when we download code in flash, Please explain in steps?

Thanks / Shailesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Your operation is totally wrong.

Now, ignore all your operation, follow me to test my .s19 code at first.

1. download the package which I send you yesterday:

In folder :evkbimxrt1050_hello_world\Debug

You will find this file:evkbimxrt1050_hello_world.s19

2. Download the MCUBootutility tool

You will find this tool is really very useful and easy to use after you familiar with our RT chip, I just want to guide you to the correct way which will make you feel things more easily.

Tool download linker:

https://github.com/JayHeng/NXP-MCUBootUtility/archive/refs/tags/v3.3.0.zip

the related user manual is:

https://github.com/JayHeng/NXP-MCUBootUtility

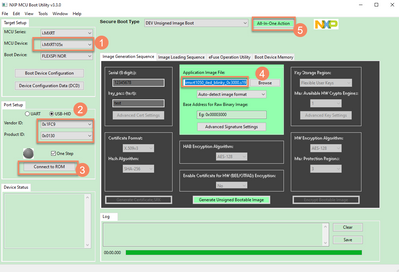

3. Use MCUBootUtility tool download code

MIMXRT1050-EVKB board configuration: SW7:1-OFF 2-ON 3-OFF 4-ON.

Press the reset button, let the board enter the serial download mode, find another USB cable also connect to the PC and the board J9.

Open the MCUbootUtility tool:

NXP-MCUBootUtility-3.3.0\bin\NXP-MCUBootUtility.exe

Step4 select my .s19 files, then step5 used to download the code.

Please try it.

After download finished.

Switch SW7:1-OFF 2-ON 3-ON 4-OFF

pressed the reset button, will enter the internal boot mode again, then use the console to check your USRT printf information.

You will find the watchdog reset happens:

Please make this method works at first.

The IAR RAM debug method is really have the RTWDOG reset issues, I know it. So I generate the RAM code and download to the flash and run it, please note, this still the RAM code, just boot from the flash.

After you make it works, I will tell you more about the IAR situation.

To your method, RAM code can't use the JLINK download, RT RAM code flashing is a little complicated.

You need to use my method.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

I am able to perform your hello world rtwdog code in run mode. It reset correctly.

Please let me know for IAR toolchain. Does it requires s.19 ? or it supports .bin file also.

Thanks / Shailesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @shaileshnsec ,

You are Good!

Now, follow me to generate the .s19 file for the IAR.

In IAR project, MIMXRT1052xxxxx_ram.icf, modify the interrupt and the text code like this:

define symbol m_interrupts_start = 0x00003000;

define symbol m_interrupts_end = 0x000033FF;

define symbol m_text_start = 0x00003400;

define symbol m_text_end = 0x0001CFFF;

Then, before you build, configure the output file as .srec, it is just the .s19

Ok, use the generated .srec app associated with MCUBootUtility tool to download your own iar .srec, check the function again.

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Kerry,

Now I am able to test in RUN mode for other IAR code.

Thanks /Shailesh