- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MX RT クロスオーバーMCU

- :

- Re: IMXRT1062 Hardfault Reading CAN3 ERFCR Register

IMXRT1062 Hardfault Reading CAN3 ERFCR Register

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

IMXRT1062 Hardfault Reading CAN3 ERFCR Register

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

According to the 1060RM setting the ERFCR will enable the Enhanced FIFO. However when I try to even read the register in the FLEXCAN example it throws a hard fault. When I tried it in my own application on a imxrt1062 I also get a hard fault at that register address. Needless to say I can't set it either.

So the question is, what is the cause of the issue and is Enhanced FIFO even enabled and the RM is incorrect?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Tom,

You asked:

> Were you able to automate that, or did you check all the addresses manually, like I did?

I didn't spend much time in this - I only used Keil's (uVisions) "memory" window, configured for 32-bit memory locations, narrowed the window to have only one 32-bit word per line so I could rapidly click through the vertical scroller, looking for addresses that don't show "????????". A bit tricky because the memory window surrenders on the first unreadable location, so you really need to step through the addresses by 4. But it only took a few minutes, and I was a bit surprised to find so many undocumented registers in the CAN-FD-capable FlexCAN3.

Hooking into HardFault_Handler to set a flag and return from it, and uses an address-scanning loop is indeed to much effort. Before doing that, I'd try other things (unless NXP come up with a solution, which hopefully happens soon):

(a)

Some of the FlexCAN registers keep their values even during a reset of the peripherals. Maybe the bit that enables the 'Enhanced' registers needs this kind of 'partial reset' (of the FlexCAN3 peripheral) to become effective. I did't check this myself, I'm having enough trouble to get CAN FD with baudrate switch to 4 MBit / second running properly. Lots of Error frames on the bus, possibly because the time quantum (tQ) is too large without the 'Enhanced' registers / more bits for "tseg1" and "tseg2".

(b)

Check if the "Supervisor" bit is improperly set when CAN_MCR is written. I'd expect a HardFault when trying to set that register without 'Supervisor' access but you never know. Maybe the access is silently ignored - I haven't got a clue. From the manual (chapter about "CANFD/FlexCAN3", quoted from the RT1064 Reference Manual) :

> The access type can be Supervisor (S) or Unrestricted (U). Most of the

> registers can be configured to have either Supervisor or Unrestricted access by

> programming the SUPV field in the MCR register.

Cheers,

Wolfgang.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Sorry all that I have been MIA but been busy with working on my other projects while waiting for Kerry to get back to us.

Thanks Wolfgang for verifying more of the registers.

Tom you are absolutely right we have been at this for over 3 months and almost 2 weeks since it was sent to NXP internal side.

Kerry is there any way to get some sort of status on the question?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Michael Smorto ,

You don't need to create the new case, I will continue to help you in this post, it doesn't matter.

Which SDK version you are using? Do you try the newest SDK, whether you can reproduce the same problem with newest SDK for RT1060? Please update your issue project with the newest SDK, then I will find time to help you to check it, thanks a lot for your undertanding.

Kerry

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I wrote:

> I'd suggest you try to print ALL the registers and see if the map matches the IMXRT or if it

> somehow matches the S32R27 one.

I've got an IMXRT1060 development board now.

I'm not using any SDK. I'm directly reading the module registers using GDB. Direct reads. No NXP software involvement at all. I get the same result reading the registers from "running code". If others are able to read the registers, then it is probably due to some previous register writing that some SDK component did.

The FlexCAN module in the IMXRT1060 isn't the S32R27 one.

I can read registers starting at 0x401d8000 with offsets 0x00, 0x50, 0x80, 0x100, 0x880 and 0x97c. I get a bus error on ox980. That matches the IMXRT FlexCAN module, but not the S32R27 one.

I can read 0xc08, but 0xc0c gives a bus error. This is the same as Michael Smorto is seeing.

I can't read 0xbf0, 0xc30 or 0x3000 either. None of the registers named "Enhanced" can be read.

I've tried setting MCR[FDEN] and am making sure the module is halted. RFEN is zero. Nothing I can find makes those registers readable.

The registers are behaving as if the Supervisor/User setting is wrong. That says:

Unrestricted read and write access to supervisor registers (registers identified with

S/U in Table "Module Memory Map" in Supervisor Mode or with S only) results in

access error.

A worked code example that includes setting those registers might show what other actions are required to have these registers enabled. I can't find anything in the Reference Manual saying anything about this.

Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Tom Evans ,

Thanks for your detail information.

If you have the official board, can you try to run the offical newest SDK project flexcan driver:

SDK_2.6.2_EVK-MIMXRT1060\boards\evkmimxrt1060\driver_examples\flexcan

Can you reproduce the problem with SDK code?

If yes, please give me modifed project which is based on the SDK, then I will double check it, and discuss it in our internal side.

Kerry

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

> If you have the official board, can you try to run the offical newest SDK project flexcan driver:

No. We're not using any of your software.

Can you put two lines of code into your SDK that tries to access these registers. Just do something like the following (using whatever the SDK uses for "printf()":

printf("FlexCAN MCR Register at 0x%08x = 0x%08x\n", 0x401d8000, *(unsigned int *)0x401d8000);

printf("FlexCAN ERFCR Register at 0x%08x = 0x%08x\n", 0x401d8c0c, *(unsigned int *)0x401d8c0c);

I get this happening - the first one works, but the second one gives a bus fault:

[ 3.300280] FlexCAN MCR Register at 0x401d8000 = 0x5980000f

[ 3.302010] Thread mode exception 5, thread 0x2020b160

[ 3.302020] r0 80026084 r1 401d8c0c r2 00000000 r3 801aae7c

[ 3.302030] r12 00000001 lr 80005175 ra 8001bf96 xpsr 61000000

[ 3.302030] PANIC: BusFault

You may need to add some sort of delay between the two statements so the first print can get out before the second one traps.

Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Tom.

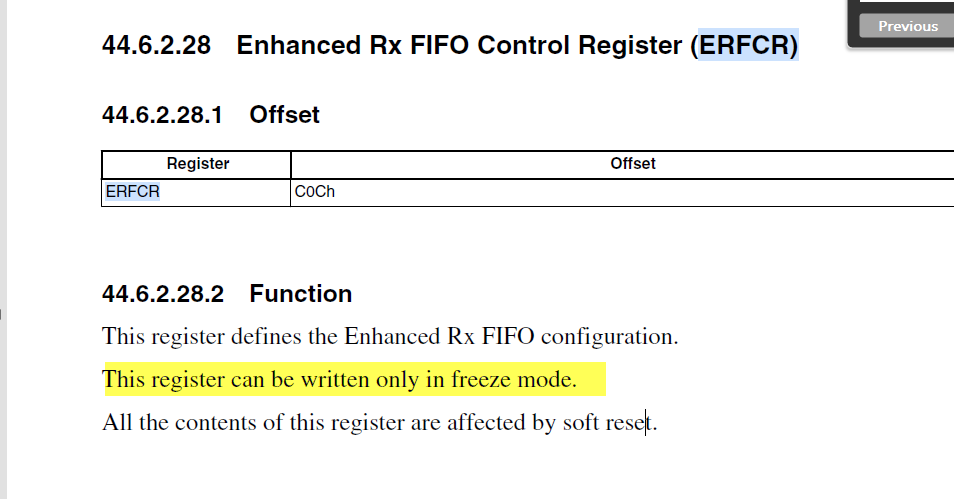

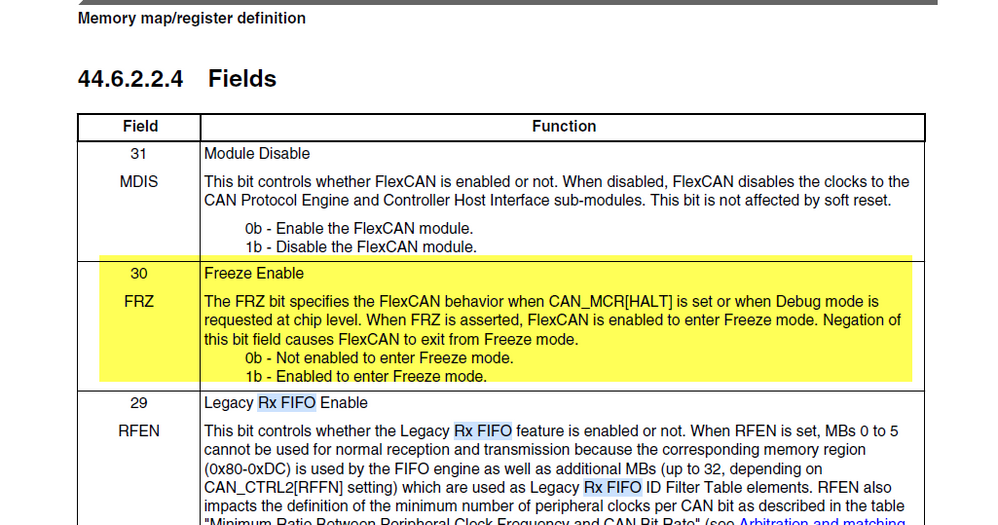

If just add your code, it really has problems when read the 0x401d8c0c, it is the ERFCR register.

Please note, when the module in freeze mode, this register is written only, it means you can't read it.

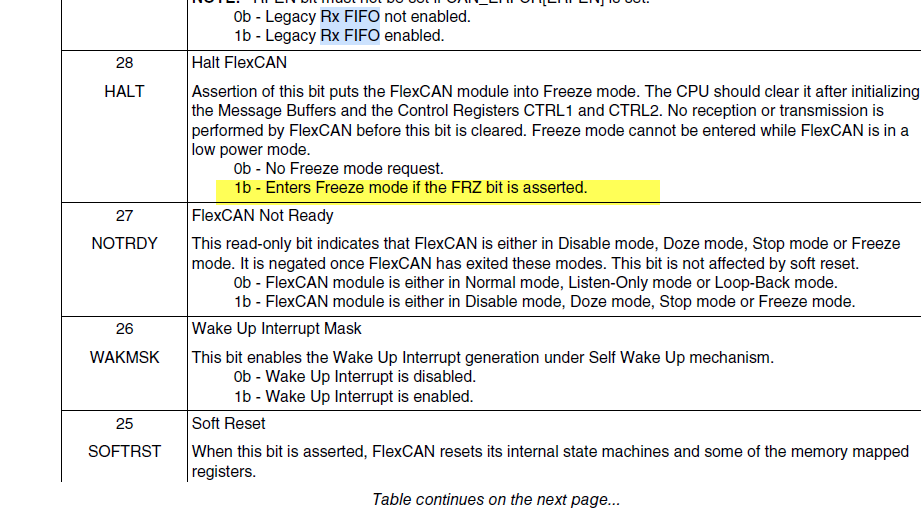

From your reply, I find your 0x401d8000 = 0x5980000f.

Please check these register:

Your bit 28, and 30 is 1, it means your flexcan module is in freeze mode, that's why you read the ERFCR have hardfault.

Please disable the freeze mode, then try to read ERFCR register again.

Wish it helps you!

Kerry

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Kerry Zhou wrote:

> > The register can only be written in Freeze Mode.

> Please note, when the module in freeze mode, this register is written only,

> it means you can't read it.

That is not what that sentence says. In English that means:

Mode | Read Access | Write Access |

Freeze | Yes | Yes |

Normal | Yes | No |

It is normal for some registers to be written only in "Freeze Mode". The Register Diagrams for all registers clearly show them all as "Read/Write". There's no "Write-Only" indications anywhere. There's nothing in the manual that says these registers can only be read in "some modes" or with "some settings".

Note that NONE of the "Extended" registers can be read. This includes ERFSR at 0x401d8c14. That is a STATUS register, which has to be read to be useful. It doesn't have the "written in freeze mode" note in its description.

(gdb) x 0x401d8000

0x401d8000: 0x5980000f

(gdb) x 0x401d8c14

0x401d8c14: Cannot access memory at address 0x401d8c14

> Please disable the freeze mode, then try to read ERFCR register again.

Did you test that? Did you set the CAN module into "Run Mode" and prove the registers can then be read? I've tested it and it doesn't work:

# Force a Soft Reset

(gdb) set *0x401d8000 = 0x2000000

# Verify MCR is now in its reset state

0x401d8000: 0x5980000f

# Turn Freeze mode off and verify it is off

(gdb) set *0x401d8000 = 0x0080000f

(gdb) x 0x401d8000

0x401d8000: 0x0080000f

# Try to read ERFCR and ERFSR

(gdb) x 0x401d8c0c

0x401d8c0c: Cannot access memory at address 0x401d8c0c

(gdb) x 0x401d8c14

0x401d8c14: Cannot access memory at address 0x401d8c14

Maybe it needs a more complicated and complete setup to be able to access those registers. Please provide working code that demonstrates the FlexCAN setup that allows register access, if that is possible.

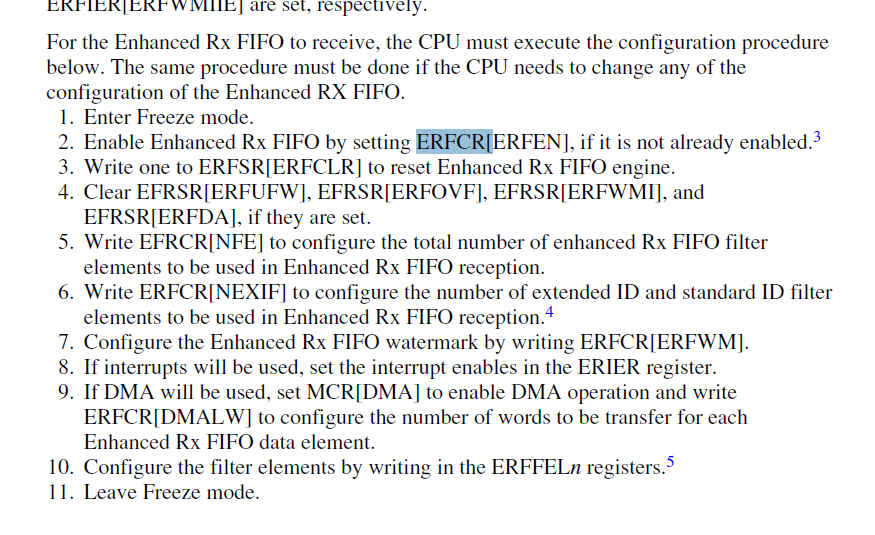

(Edit): The following says the device has to be in "Freeze Mode" to change these registers. The only requirement mentioned for the following to work is "(3) MCR[RFEN] must be cleared so that Enhanced Rx FIFO is enabled.". That bit was cleared in my tests.

44.4.7 Enhanced Rx FIFO

For the Enhanced Rx FIFO to receive, the CPU must execute the

configuration procedure below. The same procedure must be done

if the CPU needs to change any of the configuration of the Enhanced

RX FIFO.

1. Enter Freeze mode.

2. Enable Enhanced Rx FIFO by setting ERFCR[ERFEN], if it is not

already enabled. 3

3. Write one to ERFSR[ERFCLR] to reset Enhanced Rx FIFO engine.

4. Clear EFRSR[ERFUFW], EFRSR[ERFOVF], EFRSR[ERFWMI], and

EFRSR[ERFDA], if they are set.

5. Write EFRCR[NFE] to configure...

etc.Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I've been looking at other FlexCAN modules that are used in other NXP products.

This one in the IMXRT1060 looks to be the only one with the "Enhanced RX FIFO". It might be the first product to use this feature, but we'll see it more in the future.

I would imagine that the FlexCAN hardware designs have "optional features" that NXP can choose to have in a particular microprocessor (or not). Similar to all of the "optional features" that the ARM processor cores have. Features like the number of Message Buffers, the number of Masks, FD support or this new FIFO. The selected features would then need to be matched to the correct version or build of the chapter that is then put in the manual.

Here's a FlexCAN module that doesn't have the "Enhanced RX FIFO", but as a point of difference it does have 96 Mask Registers.

https://www.nxp.com/docs/en/reference-manual/MPC5746CRM.pdf

The IMXRT1060 has 64 mask registers, and doesn't respond to addresses "BASE + 980-9FC" that exists in the MPC5746 for those extra registers.

This problem could be that the IMXRT1060 was never meant to have the FIFO feature, and so this might be a "documentation mistake".

Or there could be some bits somewhere that have to be set to make these registers "appear", but having registers that could "disappear" on a reset could cause all sorts of problems with writing drivers.

Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Kerry Zhou

I have to agree with Tom E. on this. I am seeing exactly the same thing. Something is not right.

Tom Evans wrote: "Maybe it needs a more complicated and complete setup to be able to access those registers. Please provide working code that demonstrates the FlexCAN setup that allows register access, if that is possible."

I will take it one step further can you provide a working example for initializing and using FlexCAN FD FIFO. The code I provided will work up until the part I am initializing FD FIFO.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Michael Smorto,

Thanks for both of your reply.

I will contact with our internal side, just to find some code about the FD FIFO, please give me more time, thanks.

Any updated information from my side, I will let you know.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for checking Kerry. Will wait patiently. Still have plenty of other stuff to work on :smileyhappy:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Just as a note been playing with this all day with no luck.

As Tom has pointed out the problem is applicable to all extended registers. As a test I did a dump of the registers at the start of the app, it dies as soon as I try to read from one of the extended registers:

****************AT START *****************************

MCR ---- 5980000f

CTRL1 ---- 0

TIMER ---- 0

IMASK1 ---- 0

IFLAG1 ---- 0

IFLAG2 ---- 0

CTRL2 ---- 800000

ESR2 ---- 0

CRCR ---- 0

ESR2 ---- 0

FDCTRL ---- 80000100

CLOCKS

CCM_CSCMR2 ---- 13192e0e

CCM_CCGR7 ---- fffffc33

address of ERFCR -------401d8c0c

The next print i had was for the value of the ERFCR register. This is before doing anything with initializing FlexCAN.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Sorry all for the delay in getting back to you.

Tom - I couldn't find anything on "debug prints" from within the SDK source files. Also will check the references that you gave me. Also you are right I couldn't find anything about how to put it into Supervisory or user mode either - a worked example would be could.

Now I can tell you what I am using that first generated this question. I am using a Teensy 4.0 from PJRC that uses the IMXRT1062. I ported the examples for CAN FD interrupt over and it worked without a problem. Now when I went to implement FlexCAN FD FIFO I ran into the problem I described about setting the register. Reason I focused in on the ERFCR register is because its the first one called in fifo configuration function. Found it because I put basically got here prints before even attempting to read the register out to see if it changed. Putting back into the sdk just confirmed that I could not write to the register before it hung and threw a hard fault.

Also if you look in the function in the example I am not trying to read and print the register while in freeze mode. I enter freeze mode, then write to register and I get the hard fault.

Maybe this added info will help.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

> I am using a Teensy 4.0 from PJRC that uses the IMXRT1062.

Neat little board. So much promise. I thought these little boards were "programmed" simply by connecting working modules together on a screen - "no programming required". Or at least minimal programming because they came with working drivers (libraries) for everything. Do you mean it doesn't have fully working libraries for every single module on the IMXRT1062, and supporting every mode (of all the timers, all the network interfaces, USB, all the FlexPWM setups and every possible DMA configuration as well as all the CPU power and sleep modes? :-).

That's going to take some doing and take a while. For something as simple as an SPI driver (that you'd hope would be simple), the NXP sample SDK code takes about 2000 lines of code. That's because the LPSPI module is very capable, but also very complicated.

Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Tom

Not quite as easy as connecting modules up on a screen. It uses the Arduino IDE as front end but it has its own installer and compilers etc. 99% of it is done through the use of libraries to access all the modules.

Actually the T4 has been in beta testing/development since January of this year. We have been working on the drivers(libraries) since its release. Still stuff to do but the big stuff is there: SPI (DMA and non-DMA) - supports SPI transactions, PWM (flexPWM), Analog(ADC), Temperature Monitoring, FlexIO, USB, I2S, SAI, MQS, I2C, Serial ports (got 7 of those to play with). Of course with not all the chips broken out. Oh just a note - SPI on the T4 takes a lot less lines. Of course some things still need to be to be but all the major pieces are there - no I don't work for PJRC - just a hobbyist.

Right now we (another guy and me) got a FlexCAN 2.0 lib working (on any of the 3 FlexCAN ports including on the FlexCAN3 one in legacy mode). Working on the getting FlexCAN FD working. But I can not figure out how for the life of me FlexCAN-FD FIFO works or can work if you can't access those extended FIFO registers. No examples for FD-FIFO were provided so doing everything straight from the manual.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

> Oh just a note - SPI on the T4 takes a lot less lines.

Don't try to use "Continuous Mode". It doesn't seem to work.

https://community.nxp.com/message/1140267

You should also check all four SPI modes. I'm using "Mode 1" and am getting very bad clock glitches. I'm also using a positive chip-select and the NXP code generates chip-select glitches for this.

Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi guys

Is there any status on this issue. Is FIFO available for FD?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

> Is there any status on this issue.

You're too late. Because:

> - We are following threads for 7 weeks after the last post, later replies are ignored

> Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

So you'll have to open a new issue.

Did you manage to get debug prints working from the driver? Did you disassemble the code to make sure it is doing the right thing?

You printed some registers, but not enough. This chip has registers from 0x00 to 0x50, 0x880 to 0x97c, 0xbf0 to 0xc14, 0xc30 to 0xd2c and 0x3000 to 0x31fc. You should try to print out ALL the registers to try and find out which ones are and aren't working. It is possible there's a bug in the manual that is giving you the wrong addresses for some of those registers. This sort of mistake in these manuals is pretty common.

It is a good idea to compare the addresses with ones for the same module in other manuals. Looking for other NXP products with CAN FD support, finds the LPC546xx. And its controller is ... VERY different, because it is "MCAN" and not "FlexCAN". Dead end there... Searching finds the MPC5775, which has FlexCAN and FD. Except it has four FlexCAN modules, and two MCAN FD modules. Weird mix. The S32R27 has three FlexCAN controllers, two of which are FD. But they're different to the ones in the IMXRT1060. For a start, the last register is at offset 0xc08 from the base, and is CAN_FDCRC. That might match up with what you're seeing. It is possible the CAN controller in the IMXRT is documented in the S32R27 manual, and the chapter in the IMXRT manual might be wrong. There are also differences in that one uses addresses 0xAE0 to 0xAEC and the other one has different registers in the range 0xBF0 to 0xBFC. I'd suggest you try to print ALL the registers and see if the map matches the IMXRT or if it somehow matches the S32R27 one.

Do you have any files in the development environment that define the registers? Compare them to the manual. Do you have he program that NXP provides (MCUXpresso) that generates code and configurations for setting up the chip? See if it has register definitions inside it.

I've got an i.MX1050 here (not the FD one). I can read those addresses even though there's no peripheral there. But reading the registers of the one that is there works for the registers that are present (0x401d404c) but gives an exception for one that isn't (0x401d4050). So the access logic works OK. Are you sure you're not getting interference from the memory protection unit?

Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Michael Smorto,

Do you follow this procedure?

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kerry

Thanks for getting back to me.

For the easy answers. Yes I did follow the procedure the procedure that you reference from the manual including entering freeze mode before making the changes.

As for your question "Are you sure "CAN_MCR[RFEN]" isn't set?" - will have to do a double and check and let you know about that one as well as your other questions in your first post. In regards to the clocks being set, that I can say yes they are set for sure.

Thanks

Mike

EDIT:

In the app after setting the clocks (know this works - the sdk example works on my hardware). I do a call to:

FLEXCAN_FDInit(EXAMPLE_CAN, &flexcanConfig, EXAMPLE_CAN_CLK_FREQ, BYTES_IN_MB, true);

After that I do a call to my function:

FLEXCAN_SetRxEnhancedFifoConfig(EXAMPLE_CAN, true);

With that function looking like:

{

Serial.println("Entered FIFO Config");

/* Assertion. */

//assert((config) || (false == enable));

FLEXCAN_EnterFreezeMode(base);

Serial.println("Entered Freeze Mode");

{

Serial.println(CAN_ERFCR_ERFEN(1), BIN);

delay(5000);

Serial.println(base->ERFCR,BIN);

delay(5000);

base->ERFCR |= CAN_ERFCR_ERFEN(1); //Enable enhanced FIFO <======= Dies here......

Serial.println(base->ERFCR,BIN);

delay(5000);

FLEXCAN3_ERFSR = CAN_ERFSR_ERFCLR(1); //Reset RxFIFO engine

//Clear EFRSR bits

FLEXCAN3_ERFSR = CAN_ERFSR_ERFUFW(0) | CAN_ERFSR_ERFOVF(0) | CAN_ERFSR_ERFWMI(0) | CAN_ERFSR_ERFDA(0);

FLEXCAN3_ERFCR |= CAN_ERFCR_NFE(2); //Configure total number of Rx FIFO filter elements

FLEXCAN3_ERFCR |= CAN_ERFCR_NEXIF(3); // number of extended ID & standard ID filter elements

FLEXCAN3_ERFCR |= CAN_ERFSR_ERFWMI(1); // number of messages in FIFO greater than the watermark

FLEXCAN3_ERFIER = 0x01; // Enable interrupts if they are to be used

// TBD // Enable DMA operation in MCR[DMA]

//FLEXCAN3_ERFCR |= CAN_ERFCR_DMALW(1); // to configure number of words to be transfered for each data element

//Configure filter elements by writing to the ERFFELn registers?

//FLEXCAN3_ERFFEL0...127

flexcan_fd_fifo_filter_b01_t b01;

b01.fsch = 0b01;

//b01.RTRfilt = 0;

b01.std_id_flt1 = 0x000;

//b01.RTRmsk = 0;

b01.std_id_flt1 = 0x650;

FLEXCAN3_ERFFEL0 = CAN_ERFFEL_FEL(&b01);

FLEXCAN3_ERFFEL1 = CAN_ERFFEL_FEL(&b01);

}

/* Exit Freeze Mode. */

FLEXCAN_ExitFreezeMode(base);

FLEXCAN_EnableEnhancedFIFOInterrupts();

}