- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- Re: Example of flexspi_nor_config_t for GD25LX256

Example of flexspi_nor_config_t for GD25LX256

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm looking for an example of flexspi_nor_config_t found in xip/evkbimxrt1050_flexspi_nor_config.c for GD25LX256 octal flash.

What other changes do I need to make in McuXpresso IDE/Config?

1. flexspi_nor_config_t

2. Device Configuration Data [DCD].

3. Flash driver.

4. ???

Has anyone successfully booted from this device?

I'd appreciate any advice and config examples.

Thanks - Eamonn

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

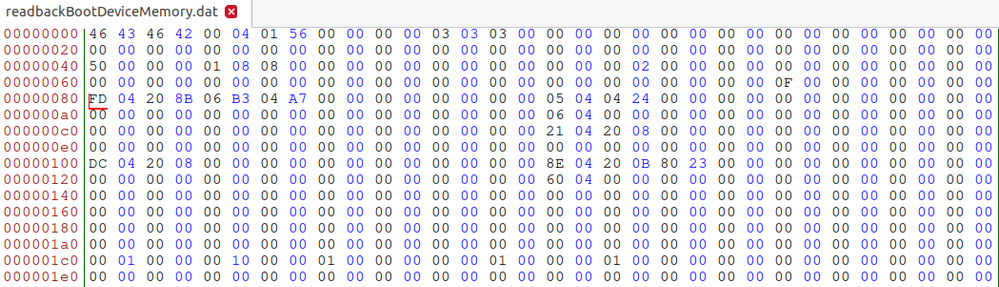

Finally got something working. I used Jay's utility to create a binary image, then compared the first 0x200 bytes of jay's image (FDCB location) with the first 0x200 of my binary, and worked back to getting a struct that gives an identical 0x200 bytes.

Here's the coded struct below... I have little idea about many of the field decisions because I can't find any docs on how to set them up correctly. This code is the very definition of a pass-it-on whisper! I do sincerely wish that NXP would release some good documentation on how to configure this struct. I don't know yet if this is an optimal configuration. Some testing required to see what performance I get.

Good info in Chapters 9 and 27 of the Reference Manual. Jay's utility can help you configure your FDCB.

Table 9.9 lists the boot pins options. Table 9.14 has the full definition of the FDCB struct. Table 9.15 has the LUT sequence definition for Serial Nor.

In a nutshell:

To get McuXpresso to program the GD25LX, set BOOT_CFG2[2:0] on your board to 0b000 (3B SPI). Big thanks to Sabina for this tip: it was crucial to allow me to program the flash via McuX. I also set up my board so I can force it into USB DFU mode (to work with Jay's utility) by having the option to pull BOOT_CFG1[6] high.

In C/C++ Build/MCU Settings, Memory details, set your Flash memory to the correct address/size, and select MIMXRT1050_SFDP_QSPI.cfx as your flash driver.

In C/C++ Build/Settings/Mcu C Compiler/Preprocessor, define the following symbols:

XIP_EXTERNAL_FLASH=1

XIP_BOOT_HEADER_ENABLE=1

McuX will automatically create the FDCB and fill it out to allow XIP booting.

If you don't need the ROM bootloader to initialize SDRAM or other peripherals, set XIP_BOOT_HEADER_DCD_ENABLE=0. If you do need SDRAM etc, then set it to 1 and you will need to provide the DCD data block also (Xpresso has a config tool for this).

I hope this is useful to anyone else booting off this flash device. Caveat: I've just got this working and there may be some bugs/mistakes in my code.

Thanks very much to Jay and Sabina for their help in solving this problem.

Eamonn

//Based on Jay Heng's McuBootUtility output configured for GD25LX:

const flexspi_nor_config_t hyperflash_config = {

.memConfig =

{

.tag = FLEXSPI_CFG_BLK_TAG,

.version = FLEXSPI_CFG_BLK_VERSION,

.readSampleClksrc=kFlexSPIReadSampleClk_ExternalInputFromDqsPad,

.csHoldTime = 3u,

.csSetupTime = 3u,

.columnAddressWidth = 0u,

.deviceModeCfgEnable = 0,

.deviceModeType = 0,

.waitTimeCfgCommands = 0,

//.deviceModeSeq = 0, //This is a flexspi_lut_seq_t sub-struct.

.deviceModeArg = 0,

.configCmdEnable = 0,

//.configModeType[0..2] = 0,

//.configCmdSeqs[3] = 0, //This an array of flexspi_lut_seq_t sub-structs.

//.configCmdArgs0..2] = 0, //Array of uint32_t.

.controllerMiscOption = 0x00000050, // Enable DDR mode, Safe configuration.

.deviceType = 0x01, //kFlexSpiDeviceType_SerialNOR

.sflashPadType = 8, //kSerialFlash_8Pads,

.serialClkFreq = 8, //kFlexSpiSerialClk_166MHz,

.lutCustomSeqEnable = 0, //LUT customization disabled.

.sflashA1Size = 0x2000000, //32u * 1024u * 1024u,

.sflashA2Size = 0,

.sflashB1Size = 0,

.sflashB2Size = 0,

.csPadSettingOverride = 0,

.sclkPadSettingOverride = 0,

.dataPadSettingOverride = 0,

.dqsPadSettingOverride = 0,

.timeoutInMs = 0,

.commandInterval = 0,

.dataValidTime = {15u, 0u},

.busyOffset = 0,

.busyBitPolarity = 0,

.lookupTable =

{

// Read LUTs as per binary from Jay Heng's MCUBootUtility configured for GD25LX...

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0xFD, RADDR_DDR, FLEXSPI_8PAD, 0x20),

FLEXSPI_LUT_SEQ(DUMMY_DDR, FLEXSPI_8PAD, 0x06, READ_DDR, FLEXSPI_8PAD, 0x04),

0,0,

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x05, READ_SDR, FLEXSPI_1PAD, 0x04),

0,0,0,

0,0,0,0,

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x06, STOP, FLEXSPI_1PAD, 0x0),

0,0,0,

0,0,0,0,

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x21, RADDR_SDR, FLEXSPI_1PAD, 0x20),

0,0,0,

0,0,0,0,

0,0,0,0,

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0xDC, RADDR_SDR, FLEXSPI_1PAD, 0x20),

0,0,0,

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x8E, RADDR_SDR, FLEXSPI_8PAD, 0x20),

FLEXSPI_LUT_SEQ(WRITE_SDR, FLEXSPI_8PAD, 0x80, STOP, FLEXSPI_1PAD, 0x0),

0,0,

0,0,0,0,

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x60, STOP, FLEXSPI_1PAD, 0x0),

},

},

.pageSize = 0x100,

.sectorSize = 0x1000,

.ipcmdSerialClkFreq = 1,

.isUniformBlockSize = 0,

.serialNorType = 0,

.needExitNoCmdMode = 0,

.halfClkForNonReadCmd = 1,

.needRestoreNoCmdMode = 0,

.blockSize = 64u * 1024u,

};

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sabina,

I succeed in getting the ROM bootloader to boot from the GD25LX by configuring flexspi_nor_config_t struct (listing below) as a 1-pad, 3-byte-address QSPI. This works and boots reliably.

Next task is to get the bootloader to switch up the GD25LX into 8-pad, 4-byte address mode.

I've been working through examples in the RM, AN12107, AN12108, AN12183, but their main focus is Hyperflash. I've studied the code documentation in xip/xxxx_flexspi_nor_config.c/h but the comments are terse one-liners. Is there any documentation out there that tells me how to build this struct?

Thanks again for all your help - Eamonn

const flexspi_nor_config_t qspiflash_config = {

.memConfig =

{

.tag = FLEXSPI_CFG_BLK_TAG,

.version = FLEXSPI_CFG_BLK_VERSION,

.readSampleClksrc=kFlexSPIReadSampleClk_ExternalInputFromDqsPad,

.csHoldTime = 3u,

.csSetupTime = 3u,

.columnAddressWidth = 0u,

.configCmdEnable = 0u,

.controllerMiscOption = 0u,

.deviceType = kFlexSpiDeviceType_SerialNOR,

.sflashPadType = kSerialFlash_1Pad, //kSerialFlash_8Pads

.serialClkFreq = kFlexSpiSerialClk_100MHz, //kFlexSpiSerialClk_30MHz, //kFlexSpiSerialClk_133MHz,

.lutCustomSeqEnable = 0u,

.sflashA1Size = 32u * 1024u * 1024u,

.dataValidTime = {16u, 16u},

.lookupTable =

{

// Read LUTs

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x03, RADDR_SDR, FLEXSPI_1PAD, 0x18),

FLEXSPI_LUT_SEQ(READ_SDR, FLEXSPI_1PAD, 0x04, STOP, FLEXSPI_1PAD, 0x0),

},

},

.pageSize = 256u,

.sectorSize = 4u * 1024u,

.blockSize = 64u * 1024u,

.isUniformBlockSize = true,

};- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jay and Sabina,

I hooked up my board to Jay's MCUBootUtility, and flashed it specifying a GD25LX configuration. Flashing seems to go ok (no error messages), but the board is not booting from it.

I've taken the image file and decoded the FDCB back into an initialised struct, and below is what I get:

const flexspi_nor_config_t hyperflash_config = {

.memConfig =

{

.tag = FLEXSPI_CFG_BLK_TAG,

.version = FLEXSPI_CFG_BLK_VERSION,

.readSampleClksrc=kFlexSPIReadSampleClk_ExternalInputFromDqsPad,

.csHoldTime = 3u,

.csSetupTime = 3u,

.columnAddressWidth = 0u,

.deviceModeCfgEnable = 0,

.deviceModeType = 0,

.waitTimeCfgCommands = 0,

//.deviceModeSeq = 0, //This is a flexspi_lut_seq_t sub-struct.

.deviceModeArg = 0,

.configCmdEnable = 0,

//.configModeType[0..2] = 0,

//.configCmdSeqs[3] = 0, //This an array of flexspi_lut_seq_t sub-structs.

//.configCmdArgs0..2] = 0, //Array of uint32_t.

.controllerMiscOption = 0x00000050, // Enable DDR mode, Safe configuration.

.deviceType = 0x01, //kFlexSpiDeviceType_SerialNOR

.sflashPadType = 8, //kSerialFlash_8Pads,

.serialClkFreq = 8, kFlexSpiSerialClk_133MHz,

.lutCustomSeqEnable = 0, //LUT customization disabled.

.sflashA1Size = 0x2000000, //32u * 1024u * 1024u,

.sflashA2Size = 0,

.sflashB1Size = 0,

.sflashB2Size = 0,

.csPadSettingOverride = 0,

.sclkPadSettingOverride = 0,

.dataPadSettingOverride = 0,

.dqsPadSettingOverride = 0,

.timeoutInMs = 0,

.commandInterval = 0,

.dataValidTime = {15u, 0u},

.busyoffset = 0,

.busyBitPolarity = 0,

.lookupTable =

{

// Read LUTs as per binary...

},

},

.pageSize = 0x100,

.sectorSize = 0x100,

.ipcmdSerialClkFreq = 1,

.isUniformBlockSize = 1,

.serialNorType = 0,

.needExitNoCmdMode = 0,

.halfClkForNonReadCmd = 1,

.needRestoreNoCmdMode = 0,

.blockSize = 64u * 1024u,

};This is the FDCB:

Questions for Jay:

1. Where are you getting the information to fill out the flexspi_nor_config struct in your utility tool? I've looked through all the docs I can find, and I can't seem to find any instructions on how to properly fill out this struct. Some of the settings I find puzzling (e.g. sector size).

2. It seems GD25LX powers up in 3B address mode, and would need to be switched up to 4B mode. I assume deviceMode fields or configMode fields could be used to do the configure. Any idea how to do this?

3. Is Octal DTR SPI or DTR OPI better for performance? How would one set up the struct to ask for DTR OPI mode if that is better?

NXP has qualified the GD25LX as a viable bootable flash device. There must be a project somewhere in the vault that was used to test this device. Could this be published to provide an example for using the GD25LX?

Thanks again for your attention and kind help.

Best regards - Eamonn

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Edit: the initializer line .serialClkFreq = 8, kFlexSpiSerialClk_166MHz, should read //kFlexSpiSerialClk_166MHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Finally got something working. I used Jay's utility to create a binary image, then compared the first 0x200 bytes of jay's image (FDCB location) with the first 0x200 of my binary, and worked back to getting a struct that gives an identical 0x200 bytes.

Here's the coded struct below... I have little idea about many of the field decisions because I can't find any docs on how to set them up correctly. This code is the very definition of a pass-it-on whisper! I do sincerely wish that NXP would release some good documentation on how to configure this struct. I don't know yet if this is an optimal configuration. Some testing required to see what performance I get.

Good info in Chapters 9 and 27 of the Reference Manual. Jay's utility can help you configure your FDCB.

Table 9.9 lists the boot pins options. Table 9.14 has the full definition of the FDCB struct. Table 9.15 has the LUT sequence definition for Serial Nor.

In a nutshell:

To get McuXpresso to program the GD25LX, set BOOT_CFG2[2:0] on your board to 0b000 (3B SPI). Big thanks to Sabina for this tip: it was crucial to allow me to program the flash via McuX. I also set up my board so I can force it into USB DFU mode (to work with Jay's utility) by having the option to pull BOOT_CFG1[6] high.

In C/C++ Build/MCU Settings, Memory details, set your Flash memory to the correct address/size, and select MIMXRT1050_SFDP_QSPI.cfx as your flash driver.

In C/C++ Build/Settings/Mcu C Compiler/Preprocessor, define the following symbols:

XIP_EXTERNAL_FLASH=1

XIP_BOOT_HEADER_ENABLE=1

McuX will automatically create the FDCB and fill it out to allow XIP booting.

If you don't need the ROM bootloader to initialize SDRAM or other peripherals, set XIP_BOOT_HEADER_DCD_ENABLE=0. If you do need SDRAM etc, then set it to 1 and you will need to provide the DCD data block also (Xpresso has a config tool for this).

I hope this is useful to anyone else booting off this flash device. Caveat: I've just got this working and there may be some bugs/mistakes in my code.

Thanks very much to Jay and Sabina for their help in solving this problem.

Eamonn

//Based on Jay Heng's McuBootUtility output configured for GD25LX:

const flexspi_nor_config_t hyperflash_config = {

.memConfig =

{

.tag = FLEXSPI_CFG_BLK_TAG,

.version = FLEXSPI_CFG_BLK_VERSION,

.readSampleClksrc=kFlexSPIReadSampleClk_ExternalInputFromDqsPad,

.csHoldTime = 3u,

.csSetupTime = 3u,

.columnAddressWidth = 0u,

.deviceModeCfgEnable = 0,

.deviceModeType = 0,

.waitTimeCfgCommands = 0,

//.deviceModeSeq = 0, //This is a flexspi_lut_seq_t sub-struct.

.deviceModeArg = 0,

.configCmdEnable = 0,

//.configModeType[0..2] = 0,

//.configCmdSeqs[3] = 0, //This an array of flexspi_lut_seq_t sub-structs.

//.configCmdArgs0..2] = 0, //Array of uint32_t.

.controllerMiscOption = 0x00000050, // Enable DDR mode, Safe configuration.

.deviceType = 0x01, //kFlexSpiDeviceType_SerialNOR

.sflashPadType = 8, //kSerialFlash_8Pads,

.serialClkFreq = 8, //kFlexSpiSerialClk_166MHz,

.lutCustomSeqEnable = 0, //LUT customization disabled.

.sflashA1Size = 0x2000000, //32u * 1024u * 1024u,

.sflashA2Size = 0,

.sflashB1Size = 0,

.sflashB2Size = 0,

.csPadSettingOverride = 0,

.sclkPadSettingOverride = 0,

.dataPadSettingOverride = 0,

.dqsPadSettingOverride = 0,

.timeoutInMs = 0,

.commandInterval = 0,

.dataValidTime = {15u, 0u},

.busyOffset = 0,

.busyBitPolarity = 0,

.lookupTable =

{

// Read LUTs as per binary from Jay Heng's MCUBootUtility configured for GD25LX...

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0xFD, RADDR_DDR, FLEXSPI_8PAD, 0x20),

FLEXSPI_LUT_SEQ(DUMMY_DDR, FLEXSPI_8PAD, 0x06, READ_DDR, FLEXSPI_8PAD, 0x04),

0,0,

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x05, READ_SDR, FLEXSPI_1PAD, 0x04),

0,0,0,

0,0,0,0,

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x06, STOP, FLEXSPI_1PAD, 0x0),

0,0,0,

0,0,0,0,

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x21, RADDR_SDR, FLEXSPI_1PAD, 0x20),

0,0,0,

0,0,0,0,

0,0,0,0,

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0xDC, RADDR_SDR, FLEXSPI_1PAD, 0x20),

0,0,0,

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x8E, RADDR_SDR, FLEXSPI_8PAD, 0x20),

FLEXSPI_LUT_SEQ(WRITE_SDR, FLEXSPI_8PAD, 0x80, STOP, FLEXSPI_1PAD, 0x0),

0,0,

0,0,0,0,

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x60, STOP, FLEXSPI_1PAD, 0x0),

},

},

.pageSize = 0x100,

.sectorSize = 0x1000,

.ipcmdSerialClkFreq = 1,

.isUniformBlockSize = 0,

.serialNorType = 0,

.needExitNoCmdMode = 0,

.halfClkForNonReadCmd = 1,

.needRestoreNoCmdMode = 0,

.blockSize = 64u * 1024u,

};

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sabina, this is very helpful.

I switched to CFG_Boot2[2:0] to 0b000, tested, failed.

Next I changed the Flash driver in MCU Settings from MIMXRT1050_SFDP_HYPERFLASH.cfx to MIMXRT1050_SFDP_QSPI.cfx.

Bingo! That combination is reporting success in programming the flash. (See debugger messages below.)

I get a target crash because I haven't correctly configured the XIP FDCB (flexspi_nor_config_t) in the target code yet. That's my next challenge.

I'll try Jay's MCUBootUtility to generate the FDCB. If you have an example of this oven-ready, I'll happily take a short cut!

Thank you so much for your help.

Best - Eamonn

MCUXpresso IDE RedlinkMulti Driver v11.1 (Jul 7 2020 10:53:47 - crt_emu_cm_redlink build 5)

Found chip XML file in /home/eamonn/Documents/MCUXpresso_11.2.0_4120/workspace/pink_2/Debug/MIMXRT1051xxxxB.xml

Reconnected to existing LinkServer process.

============= SCRIPT: RT1050_connect.scp =============

RT1050 Connect Script

DpID = 0BD11477

APID = 0x04770041

Disabling MPU

Configure FlexRAM for 256KB OC RAM, 128KB I-TCM, 128KB D-TCM

Finished

============= END SCRIPT =============================

Probe Firmware: LPC-LINK2 CMSIS-DAP V5.361 (NXP Semiconductors)

Serial Number: IXFUMYIS

VID:PID: 1FC9:0090

USB Path: /dev/hidraw3

Using memory from core 0 after searching for a good core

debug interface type = Cortex-M7 (DAP DP ID 0BD11477) over SWD TAP 0

processor type = Cortex-M7 (CPU ID 00000C27) on DAP AP 0

number of h/w breakpoints = 8

number of flash patches = 0

number of h/w watchpoints = 4

Probe(0): Connected&Reset. DpID: 0BD11477. CpuID: 00000C27. Info: <None>

Debug protocol: SWD. RTCK: Disabled. Vector catch: Disabled.

Content of CoreSight Debug ROM(s):

RBASE E00FD000: CID B105100D PID 000008E88C ROM (type 0x1)

ROM 1 E00FE000: CID B105100D PID 04000BB4C8 ROM (type 0x1)

ROM 2 E00FF000: CID B105100D PID 04000BB4C7 ROM (type 0x1)

ROM 3 E000E000: CID B105E00D PID 04000BB00C Gen SCS (type 0x0)

ROM 3 E0001000: CID B105E00D PID 04000BB002 Gen DWT (type 0x0)

ROM 3 E0002000: CID B105E00D PID 04000BB00E Gen (type 0x0)

ROM 3 E0000000: CID B105E00D PID 04000BB001 Gen ITM (type 0x0)

ROM 2 E0041000: CID B105900D PID 04001BB975 CSt ARM ETMv4.0 type 0x13 Trace Source - Core

ROM 2 E0042000: CID B105900D PID 04004BB906 CSt type 0x14 Debug Control - Trigger, e.g. ECT

ROM 1 E0040000: CID B105900D PID 04000BB9A9 CSt type 0x11 Trace Sink - TPIU

ROM 1 E0043000: CID B105F00D PID 04001BB101 Sys (type 0x0)

NXP: MIMXRT1051xxxxB

DAP stride is 1024 bytes (256 words)

Inspected v.2 External Flash Device on SPI using SFDP JEDEC ID MIMXRT1050_SFDP_QSPI.cfx

Image 'iMXRT1050_SFDP_QSPI Jul 7 2020 10:54:37'

Opening flash driver MIMXRT1050_SFDP_QSPI.cfx

Sending VECTRESET to run flash driver

Flash variant 'JEDEC_SFDP_Device' detected (32MB = 512*64K at 0x60000000)

Closing flash driver MIMXRT1050_SFDP_QSPI.cfx

Connected: was_reset=false. was_stopped=true

Awaiting telnet connection to port 3330 ...

GDB nonstop mode enabled

Opening flash driver MIMXRT1050_SFDP_QSPI.cfx (already resident)

Sending VECTRESET to run flash driver

Flash variant 'JEDEC_SFDP_Device' detected (32MB = 512*64K at 0x60000000)

Writing 26152 bytes to address 0x60002000 in Flash

Sectors written: 0, unchanged: 1, total: 1

Erased/Wrote sector 0-0 with 26152 bytes in 50msec

Closing flash driver MIMXRT1050_SFDP_QSPI.cfx

Flash Write Done

Flash Program Summary: 26152 bytes in 0.05 seconds (510.78 KB/sec)

Starting execution using system reset and halt target

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Excellent! I am glad that you were able to resolve this.

Best Regards,

Sabina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jay/Sabina. Please let me know if you have any comments on my setup and the error message I'm getting.

Thanks - Eamonn

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hope you are doing well. It looks like its not able to read the parameters correctly. Therefore I believe that choosing the the CFG_Boot2[2:0] to 101 is not correct. The option is specific to the brand Micron which in this case is not a match even though the command is listed in the datasheet of the device you are using.

Could you please try with a generic option that supports 3B as the default. Looking at the datasheet it looks like the address status bit of your device is in 3-byte address mode by default.

Let me know if this results differently for you.

Best Regards,

Sabina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, so I've got my boards and all seems well. I can load code and debug a RAM application.

Now, I'm trying to set up McuXpresso 11.2.0 to load code into the GD25LX256.

To achieve this, I use the following configurion:

BOOT_MODE[1:0] = 0b10 (internal boot with GPIO override)

BOOT_CFG1[7:0] = 0b00000000

BOOT_CFG2[2:0] = 0b101 (Micron Octal DDR, command 0xFD, OPI mode) (This seems most similar to GD25, is this correct choice?)

In the Memory details section of Mcu Settings, I have added Flash at 0x60000000, size 0x2000000, and chosen MIMXRT1050_SFDP_HYPERFLASH. Correct?

When I debug, I get this error message:

MCUXpresso IDE RedlinkMulti Driver v11.1 (Jul 7 2020 10:53:47 - crt_emu_cm_redlink build 5)

Found chip XML file in /home/eamonn/Documents/MCUXpresso_11.2.0_4120/workspace/pink_3/Debug/MIMXRT1051xxxxB.xml

( 5) Remote configuration complete

Reconnected to existing LinkServer process.

============= SCRIPT: RT1050_connect.scp =============

RT1050 Connect Script

DpID = 0BD11477

APID = 0x04770041

Disabling MPU

Configure FlexRAM for 256KB OC RAM, 128KB I-TCM, 128KB D-TCM

Finished

============= END SCRIPT =============================

Probe Firmware: LPC-LINK2 CMSIS-DAP V5.361 (NXP Semiconductors)

Serial Number: IXFUMYIS

VID:PID: 1FC9:0090

USB Path: /dev/hidraw2

Using memory from core 0 after searching for a good core

debug interface type = Cortex-M7 (DAP DP ID 0BD11477) over SWD TAP 0

processor type = Cortex-M7 (CPU ID 00000C27) on DAP AP 0

number of h/w breakpoints = 8

number of flash patches = 0

number of h/w watchpoints = 4

Probe(0): Connected&Reset. DpID: 0BD11477. CpuID: 00000C27. Info: <None>

Debug protocol: SWD. RTCK: Disabled. Vector catch: Disabled.

Content of CoreSight Debug ROM(s):

RBASE E00FD000: CID B105100D PID 000008E88C ROM (type 0x1)

ROM 1 E00FE000: CID B105100D PID 04000BB4C8 ROM (type 0x1)

ROM 2 E00FF000: CID B105100D PID 04000BB4C7 ROM (type 0x1)

ROM 3 E000E000: CID B105E00D PID 04000BB00C Gen SCS (type 0x0)

ROM 3 E0001000: CID B105E00D PID 04000BB002 Gen DWT (type 0x0)

ROM 3 E0002000: CID B105E00D PID 04000BB00E Gen (type 0x0)

ROM 3 E0000000: CID B105E00D PID 04000BB001 Gen ITM (type 0x0)

ROM 2 E0041000: CID B105900D PID 04001BB975 CSt ARM ETMv4.0 type 0x13 Trace Source - Core

ROM 2 E0042000: CID B105900D PID 04004BB906 CSt type 0x14 Debug Control - Trigger, e.g. ECT

ROM 1 E0040000: CID B105900D PID 04000BB9A9 CSt type 0x11 Trace Sink - TPIU

ROM 1 E0043000: CID B105F00D PID 04001BB101 Sys (type 0x0)

NXP: MIMXRT1051xxxxB

DAP stride is 1024 bytes (256 words)

Inspected v.2 External Flash Device on SPI using SFDP JEDEC ID MIMXRT1050_SFDP_HYPERFLASH.cfx

Image 'iMXRT1050_SFDP_HYPERFLASH Jul 7 2020 10:54:44'

Opening flash driver MIMXRT1050_SFDP_HYPERFLASH.cfx

Sending VECTRESET to run flash driver

Driver V.2 dynamic startup failed - driver Init provided no flash parameters

Flash Driver V.2 startup failed - rc Ef(55): Dynamic flash driver startup failed to provide flash parameters.

Terminate (0x0, 0x0, 0x0) status 0x40 - driver reports init failure - EXTSPIJ driver rc 7000 (0x1B58)

chip initialization failed - Ef(55): Dynamic flash driver startup failed to provide flash parameters.

failed to initialize flash driver MIMXRT1050_SFDP_HYPERFLASH.cfx

Am I missing something?

Thanks - Eamonn

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ,

Hope you are doing well.

I'd like to recommend the following application note. It describes how to enable octal spi flash.

How to Enable Boot from Octal SPI Flash and SD Card

In addition I'd recommend to review the details of the datasheet of the flash that you are using. The MIMXRT1050_SFDP_HYPERFLASH.cfx is a generic driver that attempts to recognize what type of flash it is connected to. Generally, flash devices typically contain a data block describing their properties including device size, low level structure and programming details etc. These data blocks and their use are collectively known as Serial Flash Discovery Protocol or SFDP. The standard for these blocks are described by JEDEC JESD216 standard(s).

If this is possible then it should be recognized with this driver. Flashdrivers cannot detect whether QSPI or Hyperflash is fitted on a board, therefore it is the responsibility of the user to ensure the correct driver is used.

For more details, section 15.2.4 of the MCUXpresso IDE User Guide:

https://www.nxp.com/docs/en/user-guide/MCUXpresso_IDE_User_Guide.pdf

Best Regards,

Sabina

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Jay and Sabina.

Jay: impressive tool. I'll download it and try it out. I know it's only tested on Windows, but do you know if it works on Ubuntu? Meanwhile, I'll use the code to help me build a DCD block.

Sabina: I assume you mean 15.2.4 of the IDE UG? I've read both AN12107 and the RM carefully and I've based my design on these. I'm hoping that the generic driver will be able to talk to the GD25LX256 as 15.2.4 suggests. I'll expect I'll configure the BOOT_CFG2 pins to 101b, Micron Octal DDR, command 0xFD OPI mode, which seems to be the closest match to the GD25LX256. MIMXRT1050_SFDP_HYPERFLASH.cfx for the IDE flash driver.

I'm just waiting on boards to arrive and I'll pick this up again when they do.

Thank you both very much for your help. Much appreciated.

Kind regards,

Eamonn

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, thank you. I've corrected this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

RT can boot from GD25LX256, you can use my tool MCUBootUtility to download app into this flash, my tool can generate FDCB automatically, the you can refer to FDCB for flexspi_nor_config_t