- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Re: Error in comments in schematic for RT1060 EVK ?

Error in comments in schematic for RT1060 EVK ?

Error in comments in schematic for RT1060 EVK ?

When looking at the schematics for the RT1060 EVK: i.MX RT1060 Evaluation Kit|NXP

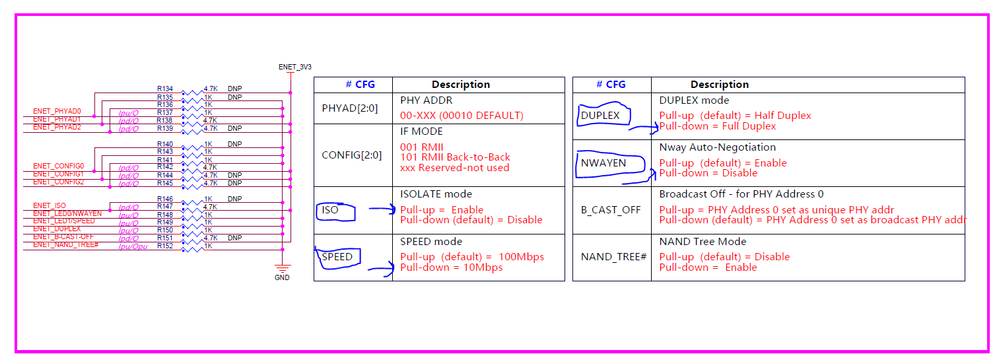

under page 10, ethernet, I think there are a couple of errors in the description of the strap settings for the KSZ8081RNB device ?

It seems that the explanation for ISO, SPEED, DUPLEX and NWAYEN are wrong (the default values are not correctly described) ?

Is the DNP/Mounted for the resistors correct or is the description ?

Also I wonder why R152 are mounted (R309 is also mounted), I would expect that the INTRP/NANDTREE# signal should be pulled up during reset ?

(The same comments are also in the schematics for 1050 EVK etc)

Hello,

The descriptions (in red) of the KSZ8081RNB configuration table are just taken

from KSZ8081RNB Datasheet.

http://ww1.microchip.com/downloads/en/devicedoc/ksz8081mnx-rnb.pdf

On the EVK scheme DNP means "Do Not Populated".

So, the default values for the EVK are not the same as mentioned in the KSZ8081RNB

Datasheet.

Note, the INTRP signal of KSZ8081RNB is open drain and requires pull up.

Resistor divider R309/R152 provides voltage level ENET_3V3 / 2, which is lower,

then Vih = 2V.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Thanks Yuri,

I was not aware that the comments in the box was for the Phy, I thought it was with reference to the resistors mounted on the EVK :smileyhappy:

However, I still wonder why the EVK has the INTRP/NANDTREE# set to low as you describe, this means that NANDTREE is activated during reset, is that correct ?

Also, as R309/R152 puts the INTR/NANDTREE# at half supply (which will be detected by low by the CPU), what will drive the INTRP signal to full high level (as the signal from the Phy is a open drain), in other words, will the INTRP signal not just change between 3.3V / 2 and 0V ?

(sorry for the many questions, just trying to maximize the chance the the PCB works the first time :smileyhappy:)

thats also what I would have expected, but on my 1060,1064, 1050 EVK boards both resistors are mounted, hence my question!

Agree Yuri,

I measured the INTRP signal, it goes fine to 3.3V although I don't understand how it can go that high with the two resistors and the output of the Phy being an opendrain output.

Anyway, I tried removing R152, and that seems to be working fine (as expected).

I just hate it when there are things that are not totally clear and well explained :smileyhappy: