- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Cant initialize SDRAM with DCD

Cant initialize SDRAM with DCD

Hi, we have a custom board using an RT1020 connected to an SDRAM. The SDRAM is specifically the ISSI IS42S81600F-7TL. We ran the SDK example called "evkmimxrt1020_semc". The example was successfully executed with no error in all tests. We modified the values of the semc_sdram_config_t struct used to setting up the parameters for SEMC. We used the following values according to SDRAM datasheet.

status_t BOARD_InitSEMC(void)

{

semc_config_t config;

semc_sdram_config_t sdramconfig;

uint32_t clockFrq = EXAMPLE_SEMC_CLK_FREQ;

/* Initializes the MAC configure structure to zero. */

memset(&config, 0, sizeof(semc_config_t));

memset(&sdramconfig, 0, sizeof(semc_sdram_config_t));

/* Initialize SEMC. */

SEMC_GetDefaultConfig(&config);

config.dqsMode = kSEMC_Loopbackdqspad; /* For more accurate timing. */

SEMC_Init(SEMC, &config);

/* Configure SDRAM. */

sdramconfig.csxPinMux = kSEMC_MUXCSX0;

sdramconfig.address = 0x80000000;

sdramconfig.memsize_kbytes = 16 * 1024; /* 16MB = 16*1024*1KBytes*/

sdramconfig.portSize = kSEMC_PortSize8Bit;

sdramconfig.burstLen = kSEMC_Sdram_BurstLen1;

sdramconfig.columnAddrBitNum = kSEMC_SdramColunm_10bit;

sdramconfig.casLatency = kSEMC_LatencyTwo;

sdramconfig.tPrecharge2Act_Ns = 15; /* Trp 15ns */

sdramconfig.tAct2ReadWrite_Ns = 15; /* Trcd 15ns */

sdramconfig.tRefreshRecovery_Ns = 67; /* Use the maximum of the (Trfc , Txsr). */

sdramconfig.tWriteRecovery_Ns = 12; /* 12ns */

sdramconfig.tCkeOff_Ns =

42; /* The minimum cycle of SDRAM CLK off state. CKE is off in self refresh at a minimum period tRAS.*/

sdramconfig.tAct2Prechage_Ns = 37; /* Tras 37 */

sdramconfig.tSelfRefRecovery_Ns = 67;

sdramconfig.tRefresh2Refresh_Ns = 60;

sdramconfig.tAct2Act_Ns = 60;

sdramconfig.tPrescalePeriod_Ns = 160 * (1000000000 / clockFrq);

sdramconfig.refreshPeriod_nsPerRow = 64 * 1000000 / 8192; /* 64ms/8192 */

sdramconfig.refreshUrgThreshold = sdramconfig.refreshPeriod_nsPerRow;

sdramconfig.refreshBurstLen = 1;

return SEMC_ConfigureSDRAM(SEMC, kSEMC_SDRAM_CS0, &sdramconfig, clockFrq);

}

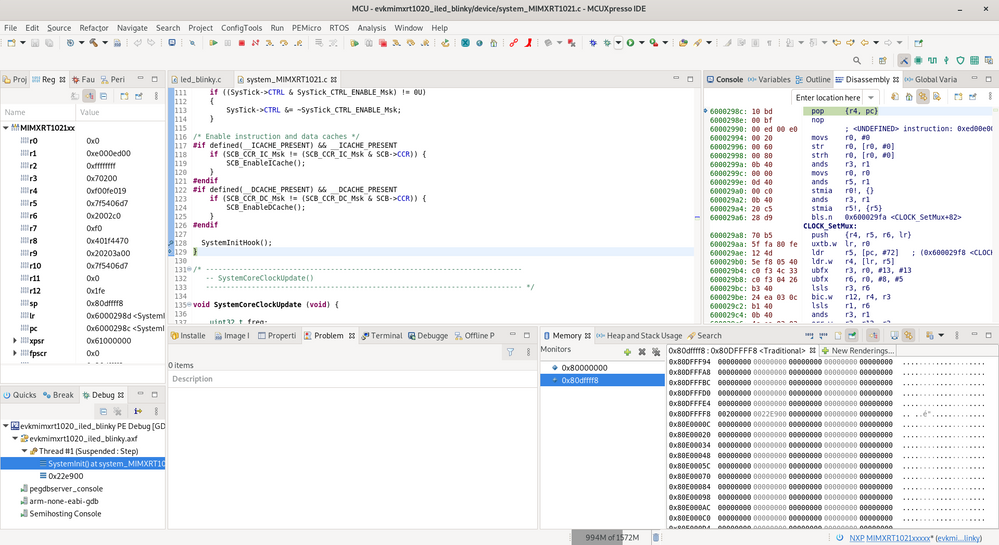

The SDRAM seems to work OK at this point. Then, when we want to create a DCD for the ROM to initialize the SDRAM to use it as main memory (stack + heap + .data + .bss) we get a Hard Fault on startup (before main function). I attached the DCD we used. The following screenshot is the point before a Hard Fault is triggered

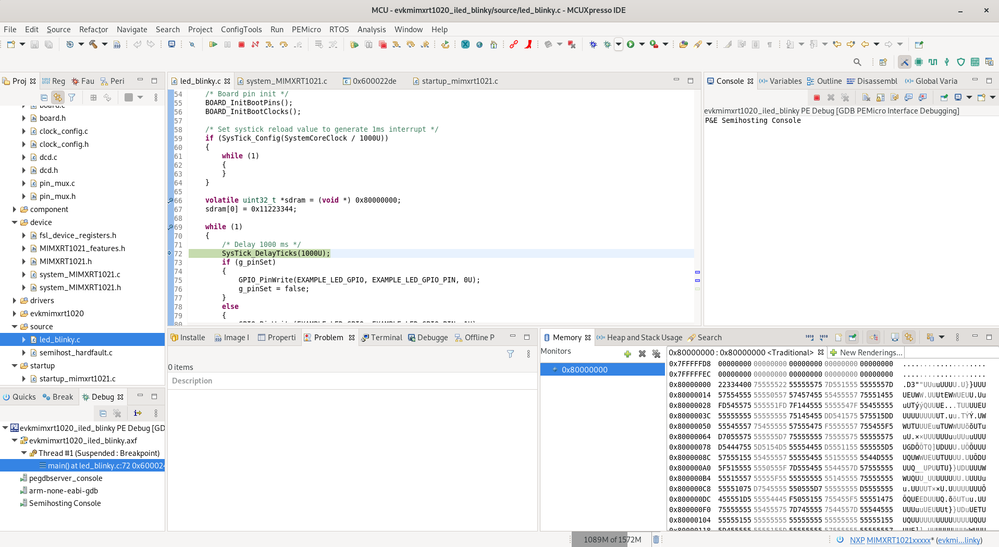

Using the "Memory" window when we write the value 0x11223344 at address 0x80_000_000 and initialize the SEMC inside the main function in ""evkmimxrt1020_semc"" example we see that it is written correctly.

When we do the same using DCD configuration we can clearly see that it is not written correctly. (Look at adress 0x80_000_000 in memory window)

We have reviewed the DCD over and over again. Is there anything we are not considering?

Our problem seems to be to build a DCD according to the configuration we used in the example.

已解决! 转到解答。

Hello @gtalocchino again,

Since the CAS Latency you set is 2. So the mode register should be 0x20 in the dcd.c file.

/* #7.1, command: write_value, address: SEMC_IPTXDAT, value: 0x20, size: 4 */

0x40, 0x2F, 0x00, 0xA0, 0x00, 0x00, 0x00, 0x20,

So in your dcd.c file the SEMC_SDRAMCR3 register and SEMC_IPCMD register should be changed.

You can try it and re-upload your dcd.c file if it still doesn't work.

Best Regards,

Tongtong Zhai

Hello @gtalocchino ,

The sdramconfig.refreshPeriod_nsPerRow set in BOARD_InitSEMC() function you provided should be

sdramconfig.refreshPeriod_nsPerRow = 64 * 1000000 / 4096; /* 64ms/4096 */ .

Since the number of rows is 4096 in the type of chip you provide. So dcd.c should also be changed accordingly.

Best Regards,

Tongtong Zhai

Hello @gtalocchino again,

Since the CAS Latency you set is 2. So the mode register should be 0x20 in the dcd.c file.

/* #7.1, command: write_value, address: SEMC_IPTXDAT, value: 0x20, size: 4 */

0x40, 0x2F, 0x00, 0xA0, 0x00, 0x00, 0x00, 0x20,

So in your dcd.c file the SEMC_SDRAMCR3 register and SEMC_IPCMD register should be changed.

You can try it and re-upload your dcd.c file if it still doesn't work.

Best Regards,

Tongtong Zhai

Yes, that was the problem! Changing the value set in IPTXDAT from 0x30 to 0x20 (due to CAS latency = 2 selected) solved the problem. Now it works correctly. We modified also the DCD according to the number of rows of our SDRAM is 4096.

Best Regards,

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

Firstly, I'd like to know whether you ever modify the DCD to fit the SDRAM on the custom board, next, please use the hello_world demo for testing, as this demo default uses the SDRAM as the primary RAM, which means you almost don't need to change the memory configuration and MPU setting.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi Jeremy, thank you for your response. We have tried the hello world example you mentioned. We get the same error. In the first image you can see that the Hard Fault occurs when running pop {r4, pc}. If you look at the memory window at the bottom right you can see that the stack pointer retrieves from memory a value for the PC that is not in the valid range of the FLASH. This implies that the previous push operations failed (SEMC is not writing the memory properly).

And yes, we have modified the DCD to configure the registers BR0, IOCR, SDRAM0, SDRAM1, SDRAM2, SDRAM3, IPCR1, IPCR2, etc... according to the configuration required by SDRAM datasheet tested successfully with "evkmimxrt1020_semc" example. You can check this in the dcd.c I attached.

Hi,

Thanks for your reply.

It seems a bit weird, whether you can upload the whole project.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi Jeremy, I attached the project as you required. What does it mean that it looks weird? Could you be more specific?

Just to be clear our problem is that we cannot generate a DCD from the configuration parameters we use in the status_t BOARD_InitSEMC(void) function I posted above. The only difference is that our SDRAM has an 8-bit data I/O bus (supported by SEMC) and 10-bit column address (supported by SEMC) and some timing parameters.

Hi,

Thanks for your reply.

1)What does it mean that it looks weird? Could you be more specific?

-- According to your previous testing, the SDRAM hardware connection seems to be good, meanwhile, you also adjust the original DCD to fit the SDRAM chip on the custom board.

After that, the SDRAM could be initialized well via the DCD.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi @gtalocchino ,

Please upload the schematic too.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------