- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- Re: CLK_1M_ERR_ FL is set while enabling 1MHZ clock output

CLK_1M_ERR_ FL is set while enabling 1MHZ clock output

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

CLK_1M_ERR_ FL is set while enabling 1MHZ clock output

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This particular bit CLK_1M_ERR_ FL is set while enabling the 1MHZ clock, i could not understand the exact meaning of this particular discription.

"Flag indicates that the count_1m count wasn't reached within 1 32kHz period. This is intended as

feedback to software that the HW_ANADIG_OSC_CONFIG2_COUNT_1M_TRG value is too high for the

RC Osc frequency."

can you please help me by explaining what this particular error and why is it coming and i am referring the example code "evkbimxrt1050_flexio_i2s_edma_transfer" from where i had taken the particular lines and added in my code

void BOARD_BootClockRUN(void)

CLOCK_SetRtcXtalFreq(32768U);

/* Enable 1MHz clock output. */

XTALOSC24M->OSC_CONFIG2 |= XTALOSC24M_OSC_CONFIG2_ENABLE_1M_MASK;

/* Use free 1MHz clock output. */

XTALOSC24M->OSC_CONFIG2 &= ~XTALOSC24M_OSC_CONFIG2_MUX_1M_MASK;

/* Set XTAL 24MHz clock frequency. */

CLOCK_SetXtalFreq(24000000U);

can you also share the points on what are things need to be checked to rectify the error.

Thanks,

maniram

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi maniram nagothi

Could you clarify where do you get that error flag? The CLK_1M clock source is enabled by Clock 1MHz setting and RC oscillator setting (CLK_1M is derived from the internal RC 24MHz oscillator that must be also enabled).

The Count_1M_TRG is the one used to generate this clock (CLK_1M) with the 24MHz oscillator and an N number of 32KHz cycles. If the value set in Count_1M_Trg will not reach 1 32kHz period, then this flag is set.

Hope this helps

Best regards

Jorge Alcala

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jorge Antonio Alcala Vazquez,

while using the example code of evkbimxrt1050_flexio_i2s_edma_transfer,In the BOARD_BootClockRUN() call from the main() uses two lines of the code:

/* Enable 1MHz clock output. */

XTALOSC24M->OSC_CONFIG2 |= XTALOSC24M_OSC_CONFIG2_ENABLE_1M_MASK;

/* Use free 1MHz clock output. */

XTALOSC24M->OSC_CONFIG2 &= ~XTALOSC24M_OSC_CONFIG2_MUX_1M_MASK;

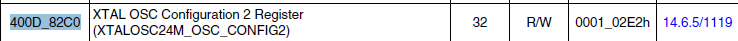

when i do a POR on the customized board and check the value at that offset the ERROR flag is set by default.

The given reset value is 0x102E2

the obtained values after the POR is 0x800102E2

can pls share the what could be the reason initially that the error flag is set?

could please share your views on this query ASAP, As i am struggling with the clock for many days.

Thanks,

Maniram

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi maniram nagothi

Please try to firstly set bit0 and bit1 of register XTALOSC24M_OSC_CONFIG0n, this is to enable RC tuning calculation logic, and then need to write a small value to COUNT_1M_TRG in register XTALOSC24M_OSC_CONFIG2_CLR, this can clear CLK_1M_ERR_FL flag. The flag is set because it has 0x2E2 which gives 1/24000000 * 738 = 1/32520

Regards

Jorge Alcala