- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- imx6ull write/read operations to spi nor flash failing in u-boot console

imx6ull write/read operations to spi nor flash failing in u-boot console

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I'm having problems accessing spi nor flash using u-boot console. Write/read operations are failing unless data size is small.

=> sf probe SF: Detected W25Q16JV with page size 256 Bytes, erase size 64 KiB, total 2 MiB => sf erase 0 0x200000 SF: 2097152 bytes @ 0x0 Erased: OK => mw.b 0x00900000 0x0 0x20000 => mtest 0x00900000 0x0090ffff 0x12345678 0x1 Testing 00900000 ... 0090ffff: Pattern 12345678 Writing... Reading...Tested 1 iteration(s) with 0 errors. =>

Write operation:

=> sf write 0x00900000 0x0 0x1000

device 0 offset 0x0, size 0x1000

SF: 4096 bytes @ 0x0 Written: OK

=>

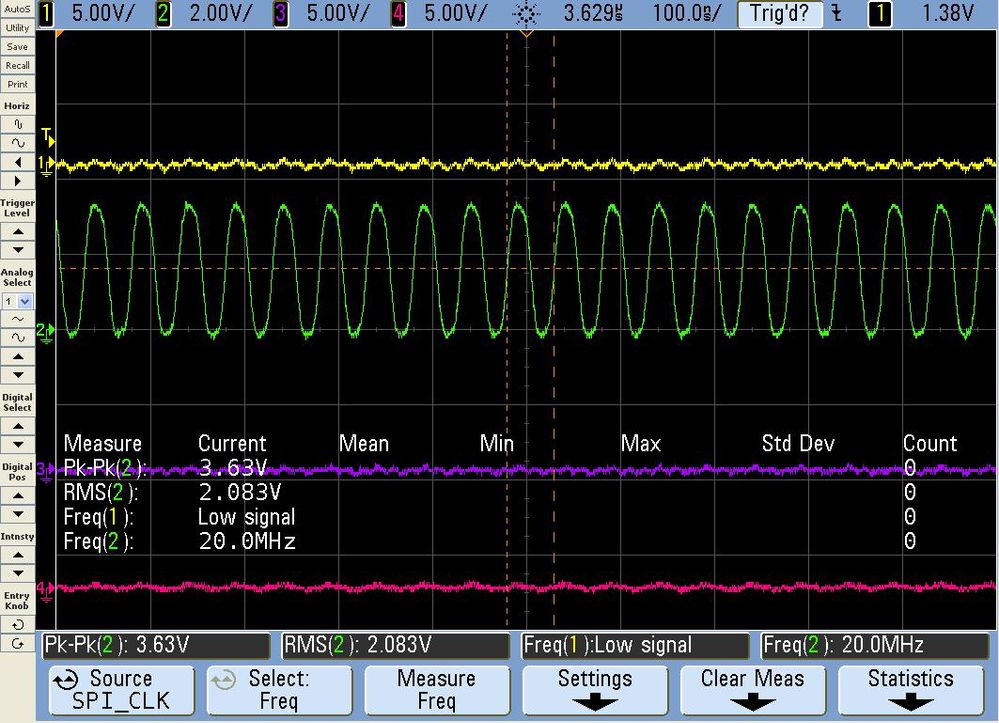

I don't know why this behavior. SPI signal levels should not decrease like that.

Read operation:

=> sf read 0x00910000 0x0 0x1000

device 0 offset 0x0, size 0x1000

SF: 4096 bytes @ 0x0 Read: OK

=>

Comapare OCRAM write buffer vs OCRAM read buffer:

=> cmp 0x00900000 0x00910000 0x1000

word at 0x00900100 (0x123456b8) != word at 0x00910100 (0xffffffff)

Total of 64 word(s) were the same

=>

64 words are ok, the rest not.

Spi nor pads are configured this way:

#ifdef CONFIG_SYS_USE_SPINOR

static iomux_v3_cfg_t const ecspi1_pads[] = {

_MX6_PAD_CSI_DATA06__ECSPI1_MOSI | MUX_PAD_CTRL(SPI_PAD_CTRL),

_MX6_PAD_CSI_DATA04__ECSPI1_SCLK | MUX_PAD_CTRL(SPI_PAD_CTRL),

_MX6_PAD_CSI_DATA07__ECSPI1_MISO | MUX_PAD_CTRL(SPI_PAD_CTRL),/* CS Pin */

_MX6_PAD_CSI_DATA05__GPIO4_IO26 | MUX_PAD_CTRL(NO_PAD_CTRL),

};static void setup_spinor(void)

{

imx_iomux_v3_setup_multiple_pads(ecspi1_pads, ARRAY_SIZE(ecspi1_pads));

gpio_direction_output(IMX_GPIO_NR(4, 26), 0);

}

Best regards

Carlos

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Carlos

regarding "signal levels" one can try to incresae drive strength

MX6_PAD_CSI_DATA pads using DSE field in IOMUXC_SW_PAD_CTL_PAD

registers, like in sect.32.6.257 SW_PAD_CTL_PAD_CSI_DATA06 SW PAD Control

Register (IOMUXC_SW_PAD_CTL_PAD_CSI_DATA06)

i.MX 6ULL Applications Processor Reference Manual

also one can check with oscillocope power supplies spi-nor flash and NVCC_CSI

power which supplies these pads according to Table 91. 14 x 14 mm Functional Contact Assignments

i.MX 6ULL Applications Processors for Consumer Products

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Igor,

we had a error in our design and for some reason the resistor that connects NVCC_CSI to DCDC_3V3 (from PMIC ) was not present. Now read/write to spi nor is working ok, and booting from spi nor too.

Thanks

Carlos

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Carlos

regarding "signal levels" one can try to incresae drive strength

MX6_PAD_CSI_DATA pads using DSE field in IOMUXC_SW_PAD_CTL_PAD

registers, like in sect.32.6.257 SW_PAD_CTL_PAD_CSI_DATA06 SW PAD Control

Register (IOMUXC_SW_PAD_CTL_PAD_CSI_DATA06)

i.MX 6ULL Applications Processor Reference Manual

also one can check with oscillocope power supplies spi-nor flash and NVCC_CSI

power which supplies these pads according to Table 91. 14 x 14 mm Functional Contact Assignments

i.MX 6ULL Applications Processors for Consumer Products

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------